Rutgers University School of Engineering

# Fall 2022

# 332:231 – Digital Logic Design

Sophocles J. Orfanidis ECE Department orfanidi@rutgers.edu

Unit 6 – Sequential circuits, latches, flip-flops

# **Course Topics**

- 1. Introduction to DLD, Verilog HDL, MATLAB/Simulink

- 2. Number systems

- 3. Analysis and synthesis of combinational circuits

- 4. Decoders/encoders, multiplexers/demultiplexers

- 5. Arithmetic systems, comparators, adders, multipliers

- 6. Sequential circuits, latches, flip-flops (Wakerly, Ch. 9 & 10)

- 7. Registers, shift registers, counters, LFSRs (Wakerly, Ch. 11)

- 8. Finite state machines, analysis and synthesis (Wakerly, Ch. 9)

Text: J. F. Wakerly, *Digital Design Principles and Practices*, 5/e, Pearson, 2018 additional references on Canvas Files > References

```

Sequential circuits (Wakerly, Ch. 9 & 10)

```

```

Topics discussed are:

```

```

Finite state machines – Mealy/Moore

```

```

State-holding elements – bistable elements

```

```

SR latches / S'R' latches

```

```

D latches

```

```

D flip-flops

```

```

T flip-flops

```

```

JK flip-flops

```

```

Converting between flip-flop types

```

## **Unit-6 Contents:**

- 1. Finite state machines Mealy/Moore

- 2. State-holding elements bistable elements

- 3. SR latch

- 4. S'R' latch

- 5. D latch

- 6. D flip-flops

- 7. T flip-flops

- 8. JK flip-flops

- 9. Converting between flip-flop types

# sequential circuits and finite state-machines are special cases of dynamic systems

In general, a system can be defined by specifying the I/O computational rule that determines the output signal y(t) from the input signal x(t).

The time variable *t* can be continuous or discrete. The system can be linear or non-linear, time-invariant or time-varying, and can be described by differential or difference equations.

State-space realizations, also known as state-space models, have a very large number of applications in many diverse fields, such as,

digital logic design differential equations for physical systems system theory electric circuits linear systems digital signal processing control systems communication systems biomedical signal processing geophysical signal processing aerospace engineering military systems statistics and time series analysis predictive analytics econometrics and financial engineering

State-space realizations are very powerful representations of systems (linear or nonlinear, time-invariant or not).

The system is described by a set of internal states at each time instant *t*, denoted for example by Q(t), and these states are used to compute the current output y(t) in terms of the current input x(t), and then update the states to their next values, Q(t+1), so that they can be used at time t+1 (or, more generally at,  $t+\Delta t$ ).

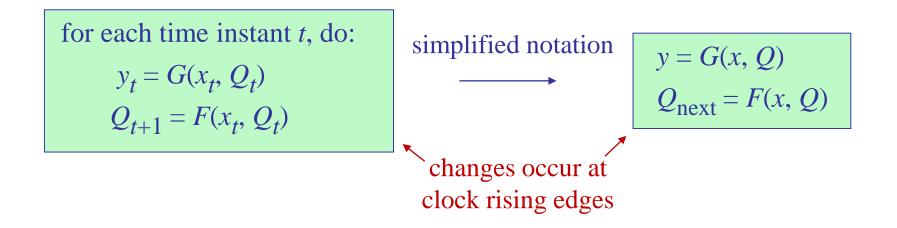

In other words, the system's time evolution is described iteratively by a computational algorithm of the form,

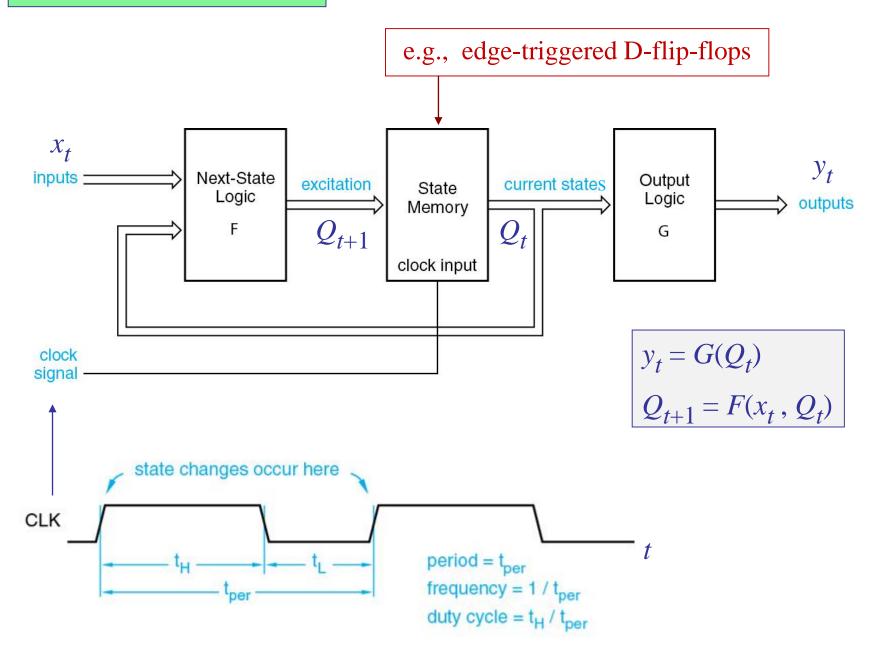

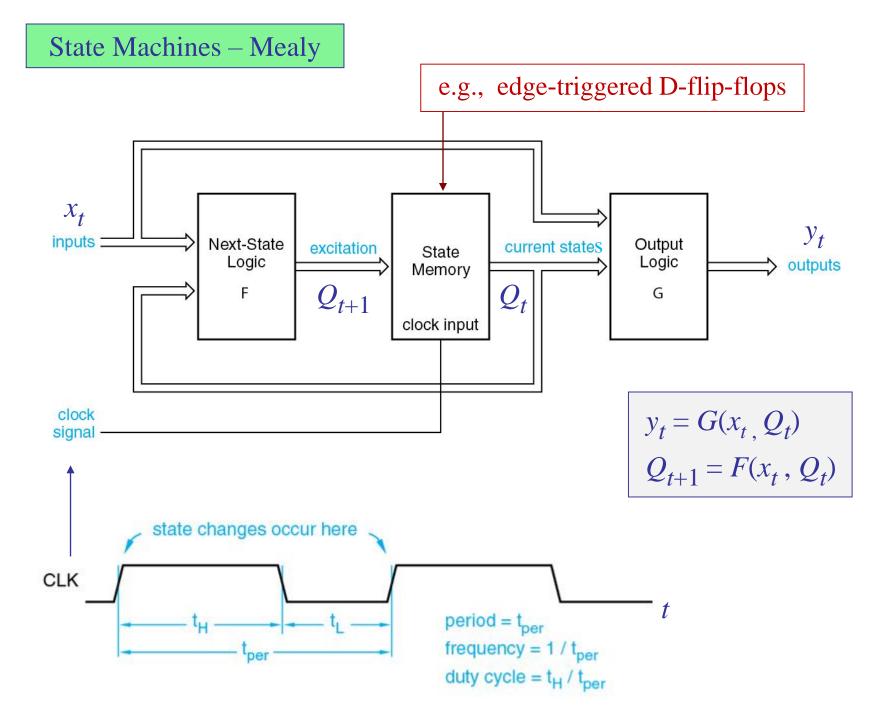

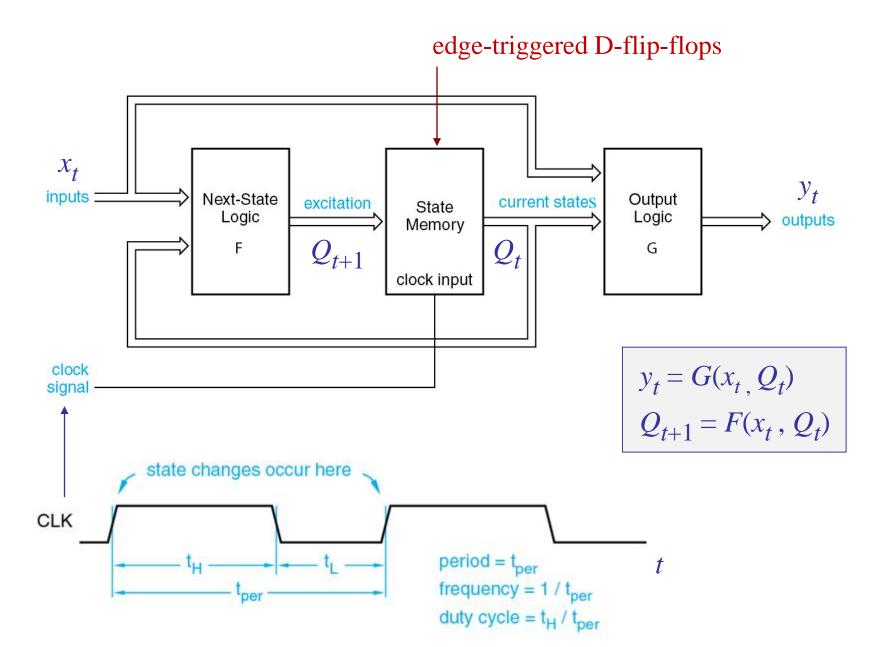

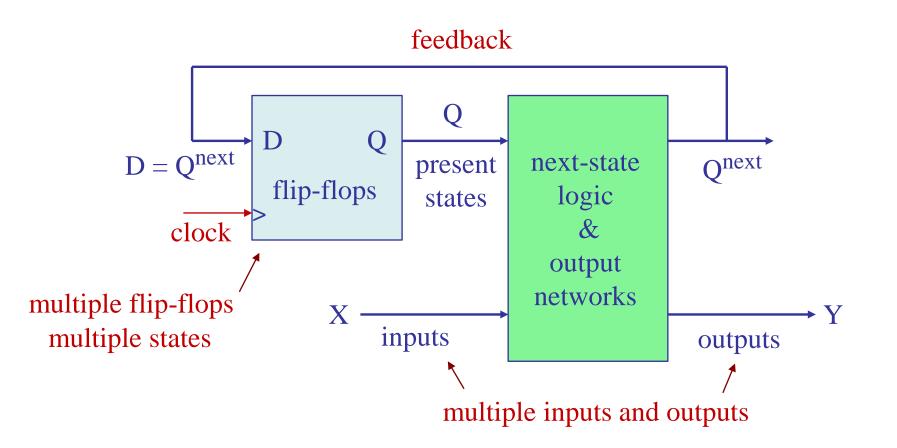

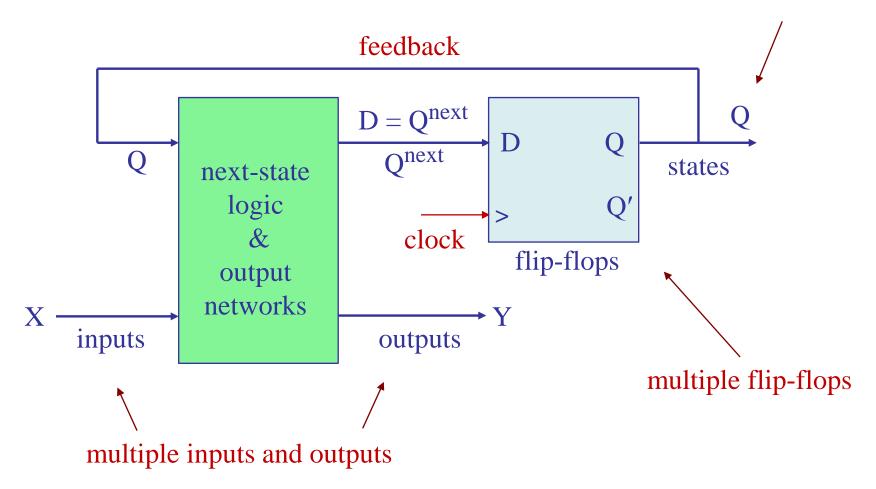

for each time instant *t*, do: y(t) = G(x(t), Q(t)) Q(t+1) = F(x(t), Q(t))

(compute output)

(update state)

[ to get started, one needs to know the initial state, Q(0), at t=0 ]

For example, in going from time *t* to time *t*+2, one carries out the steps:

at time t,

y(t) = G(x(t), Q(t))Q(t+1) = F(x(t), Q(t))

at time t+1,

y(t+1) = G(x(t+1), Q(t+1))Q(t+2) = F(x(t+1), Q(t+1))

at time t+2,

y(t+2) = G(x(t+2), Q(t+2))Q(t+3) = F(x+2), Q(t+2))

from here on, we'll use the simplified notation,  $x_t, y_t, Q_t$ for x(t), y(t), Q(t)

F() and G() depend on application

next-state logic, or excitation logic

and, G is referred to as output logic

in DLD, F is referred to as

etc.

It should be emphasized that the updated state  $Q_{t+1}$  is being computed at time *t*, and becomes available at time *t*, replacing  $Q_t$ , but it is saved until it is used later at time *t*+1.

The computations can be cast as a repetitive algorithm, in which the present state is overwritten by the next state.

initialize state *Q* (typically at *t*=0), then,

at each time t, do,

$$y_t = G(x_t, Q)$$

$Q = F(x_t, Q)$

or,

at each time t, do,  $y_t = G(x_t, Q)$   $Q_{next} = F(x_t, Q)$  $Q = Q_{next}$

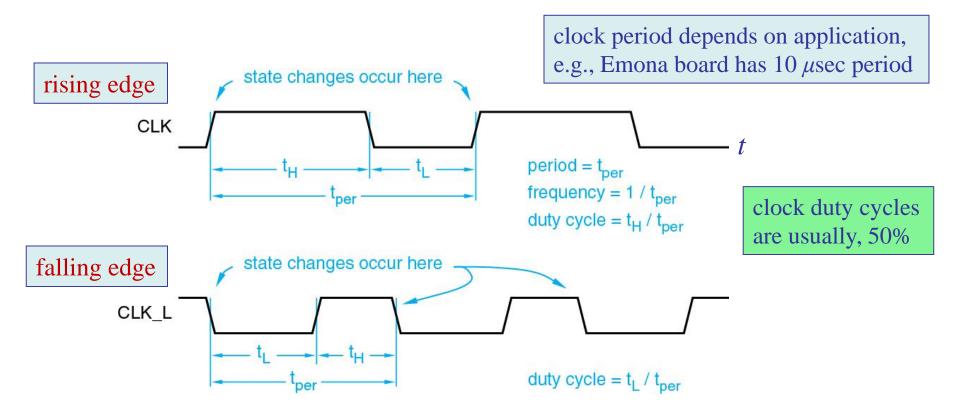

DLD notation: we assume that time is discretized in units of 1, which means one clock period, so that t+1 means one clock period ahead of t.

In DLD (essentially all) sequential circuits are synchronously driven by a clock, and the state changes occur during the rising edge of the clock period (or, alternatively - but less commonly - during the falling edge.)

State machines in DLD fall into two general families:

Moore type: output equation depends only on Q, i.e., y = G(Q)

Mealy type: output equation depends on both x and Q, i.e., y = G(x, Q)

in general, one can have multiple inputs, multiple outputs (MIMO systems), and multiple states

#### State Machines – Moore

what are state-holding elements? how to load them?

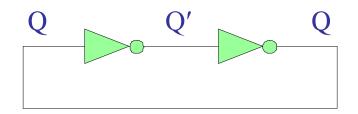

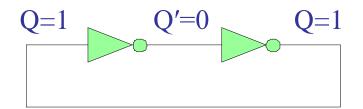

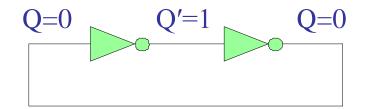

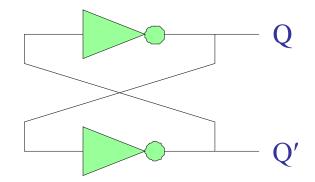

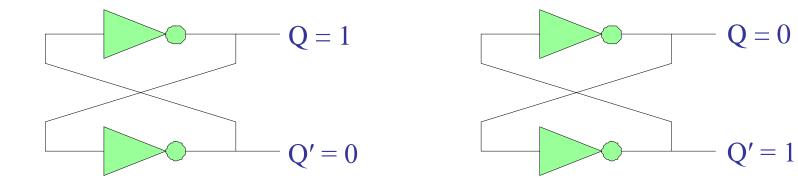

two stable states Q=1 and Q=0

two stable states - but how to load them?

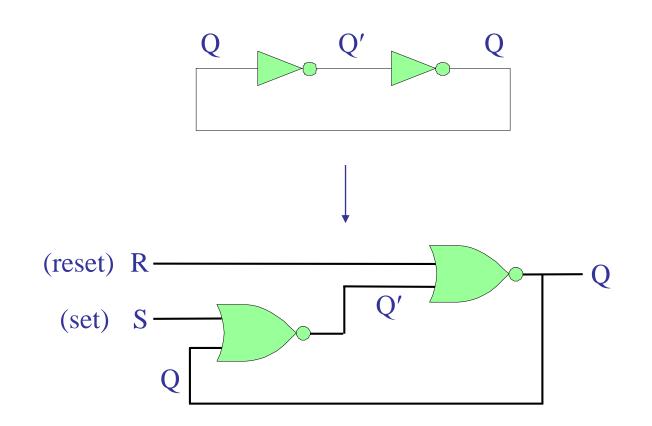

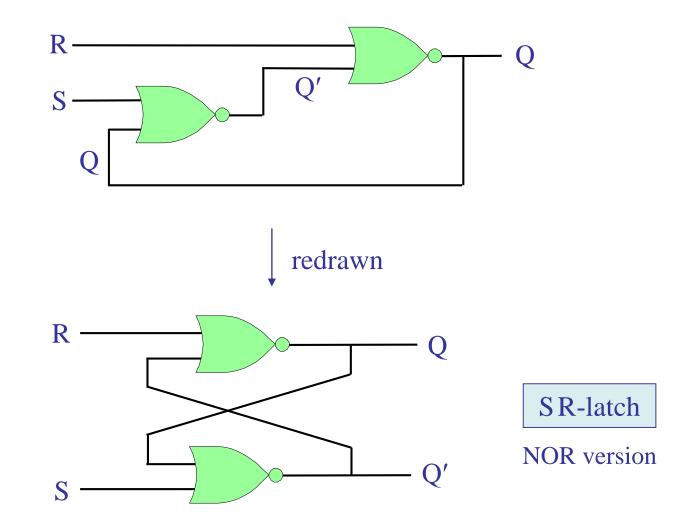

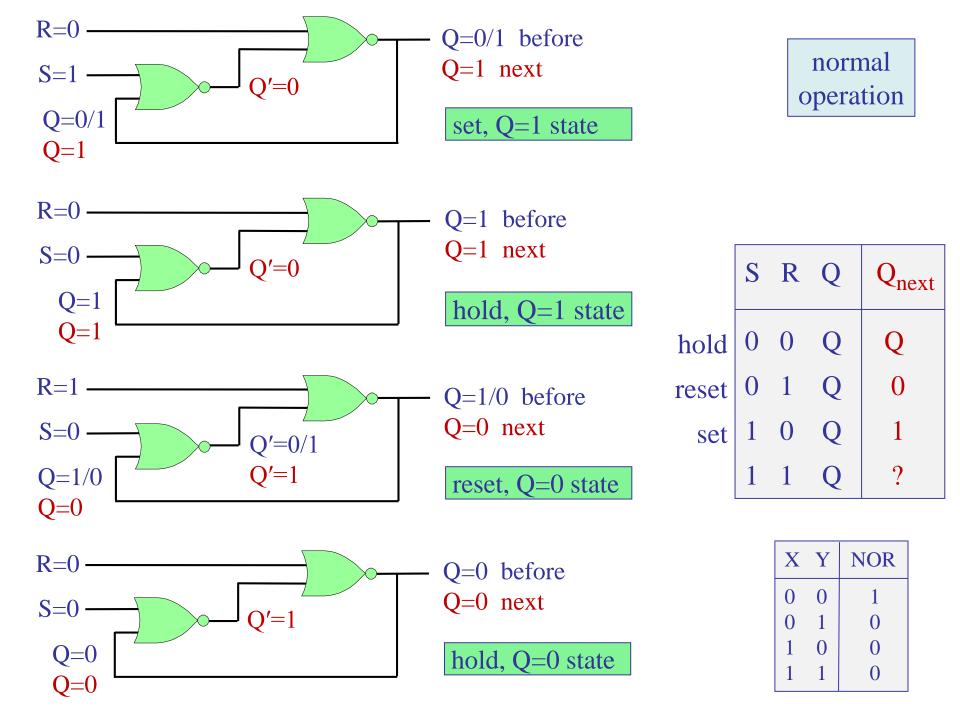

the state-loading problem is solved with **SR latches**, which provide external inputs to the bistable elements.

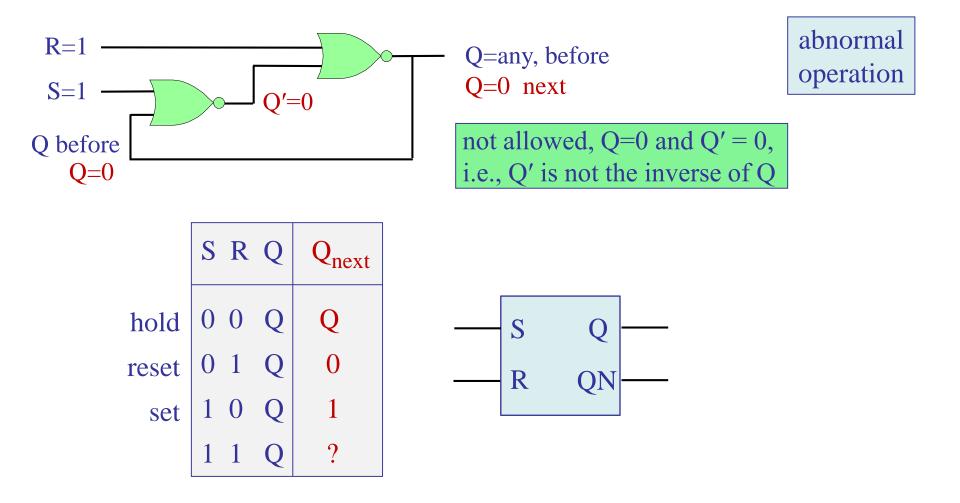

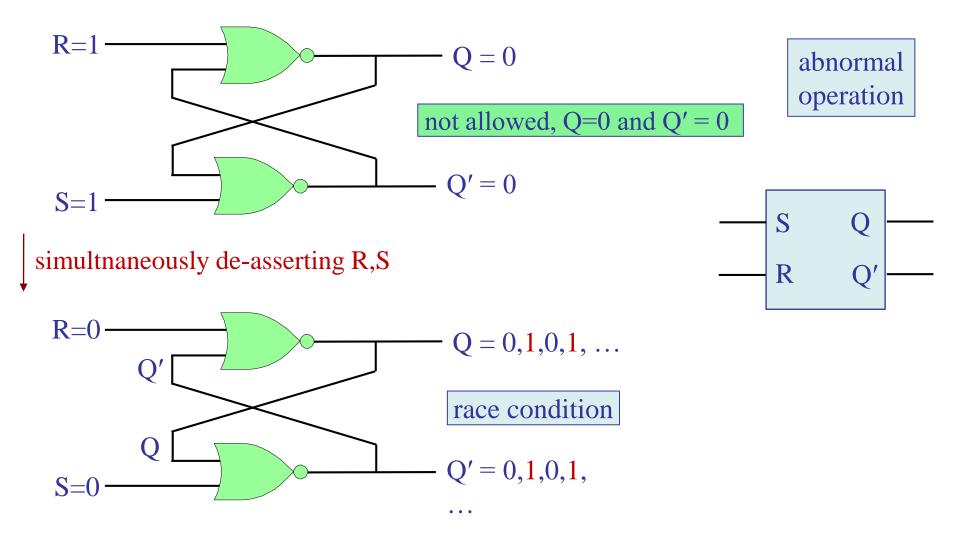

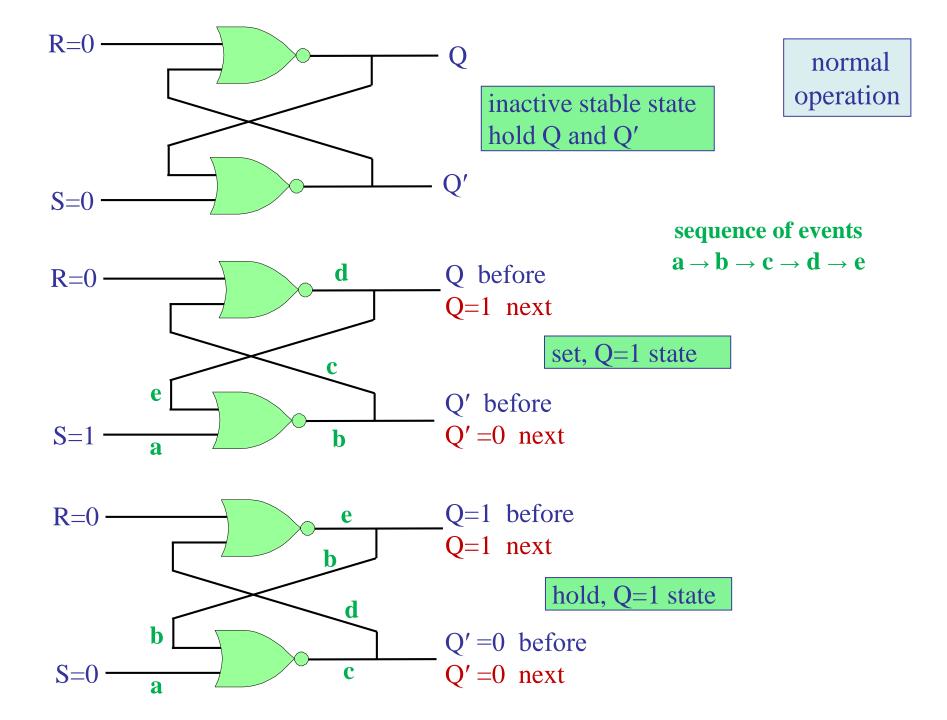

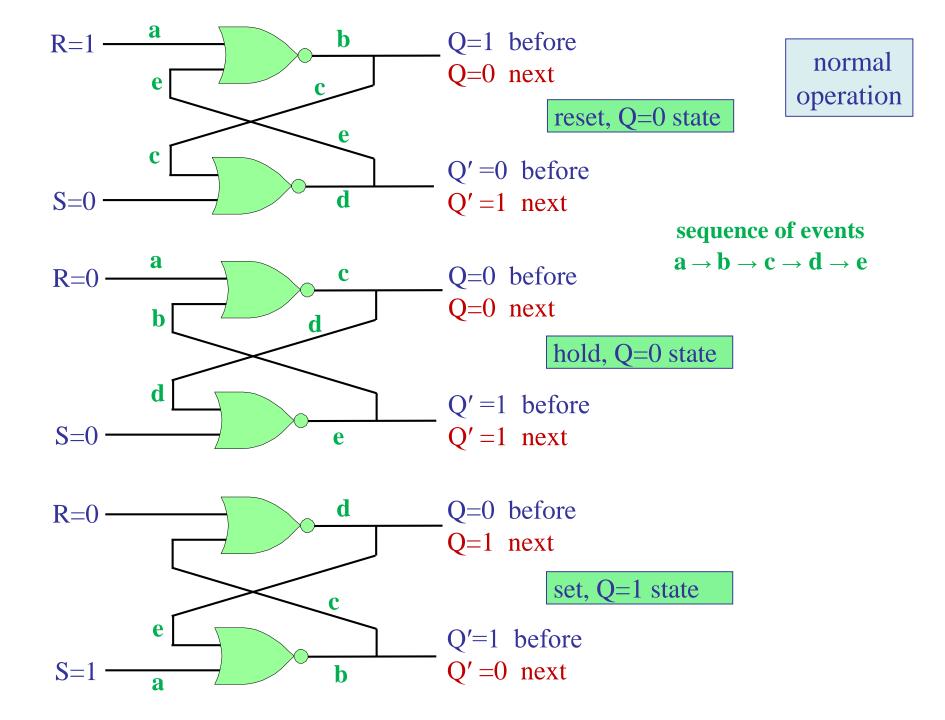

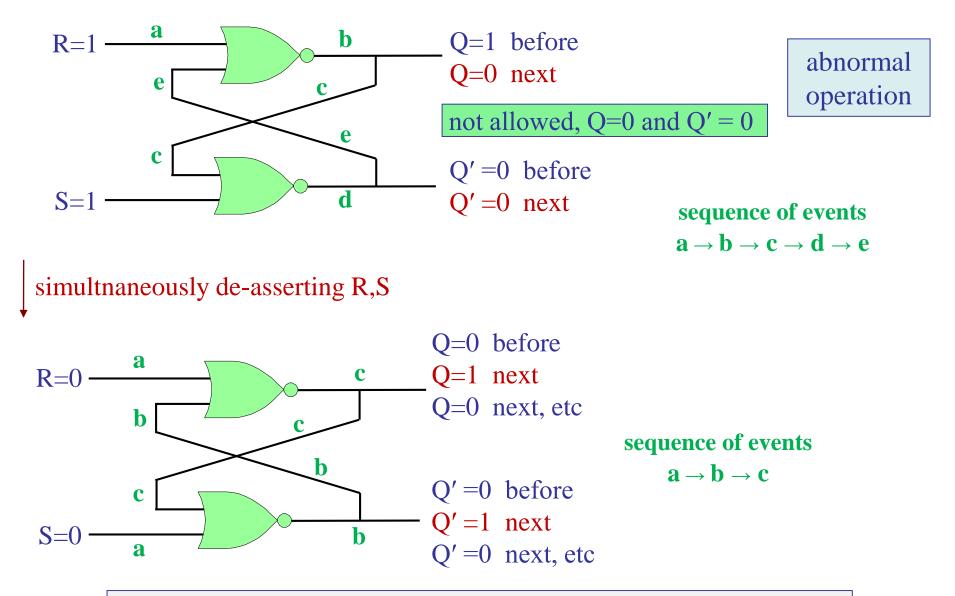

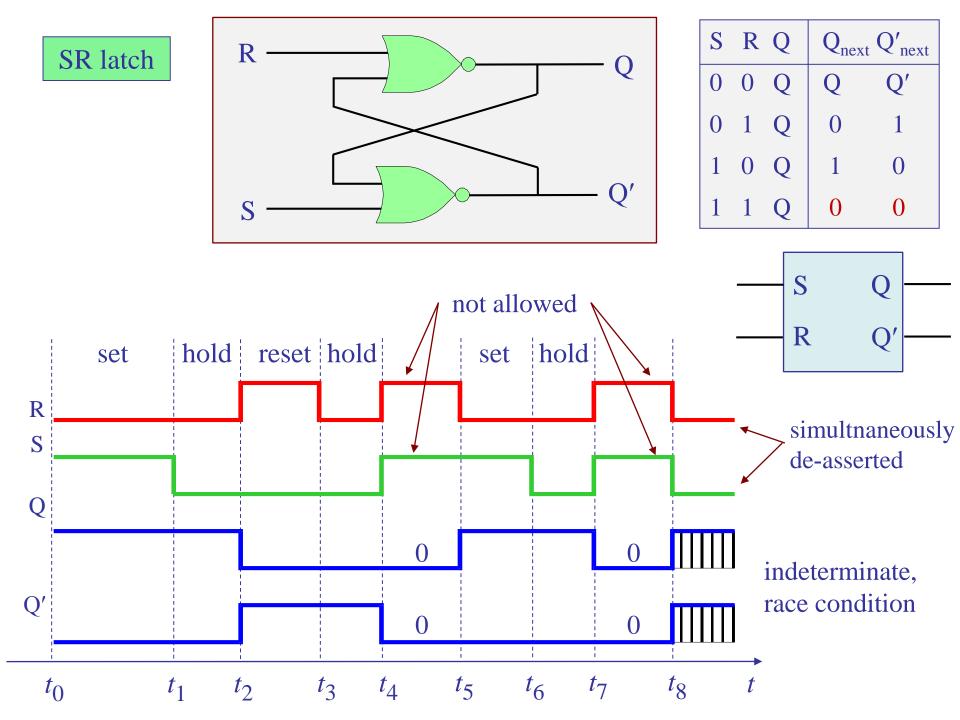

R=S=1 are not allowed because if R,S are de-asserted at exactly the same time, that is, R=S=0, then, the latch will enter into a metastable, race condition, with the Q, Q' outputs oscillating between the values 0,0 and 1,1, as explained below.

$0 \ 0 \rightarrow 1 \ 1 \rightarrow 0 \ 0 \rightarrow 1 \ 1 \dots$

R=S=1 are not allowed because if R,S are de-asserted at exactly the same time, that is, R=S=0, then, the latch will enter into a metastable, race condition, with the Q, Q' outputs oscillating between the values 0,0 and 1,1, as seen above.

$0 \ 0 \rightarrow 1 \ 1 \rightarrow 0 \ 0 \rightarrow 1 \ 1 \dots$

latch enters into a metastable, race condition, with the Q, Q' outputs oscillating between the values 0,0 and 1,1

$0 \ 0 \rightarrow 1 \ 1 \rightarrow 0 \ 0 \rightarrow 1 \ 1 \dots$

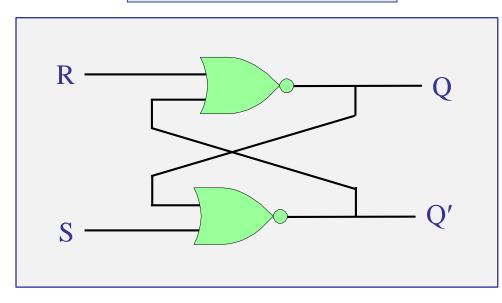

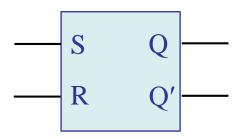

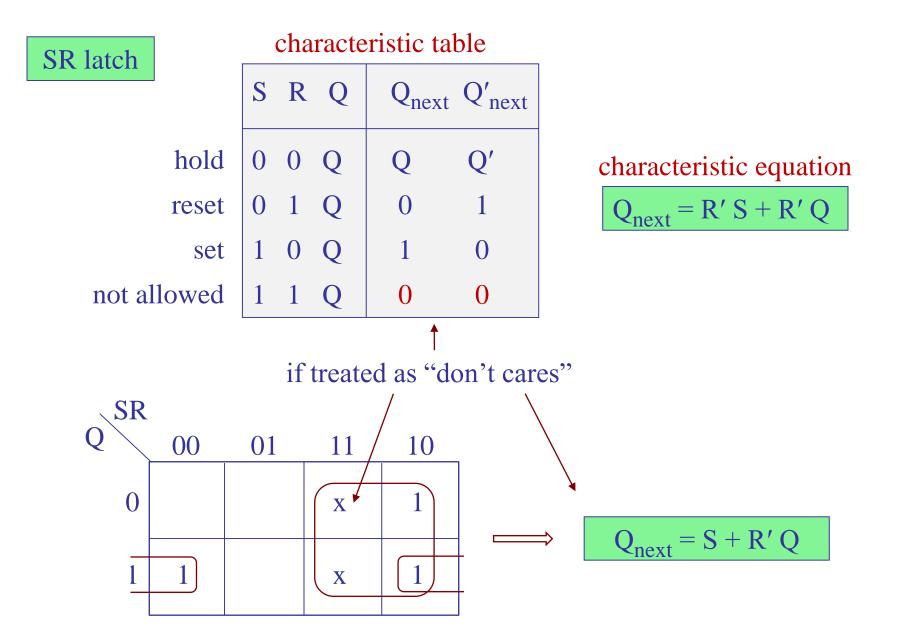

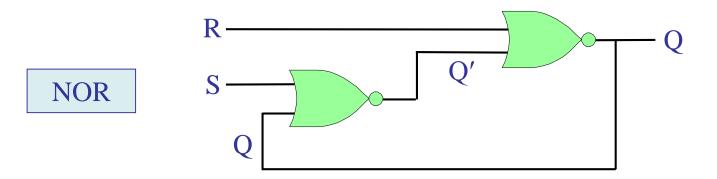

## SR latch

## NOR implementation

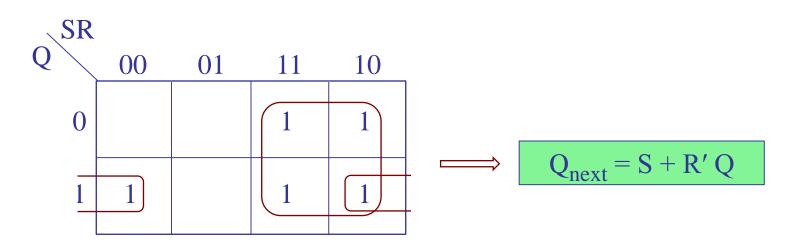

|             | S R | Q | Q <sub>nex</sub> | t Q' <sub>next</sub> | characteristic equation         |

|-------------|-----|---|------------------|----------------------|---------------------------------|

| hold        | 0 0 | Q | Q                | Q′                   | $Q_{next} = R' S + R' Q$        |

| reset       | 0 1 | Q | 0                | 1                    |                                 |

| set         | 1 0 | Q | 1                | 0                    | but with these as "don't cares" |

| not allowed | 1 1 | Q | 0                | 0                    | $Q_{next} = S + R' Q$           |

characteristic table

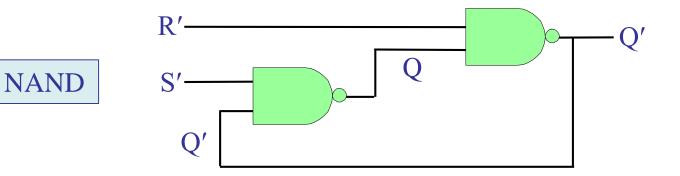

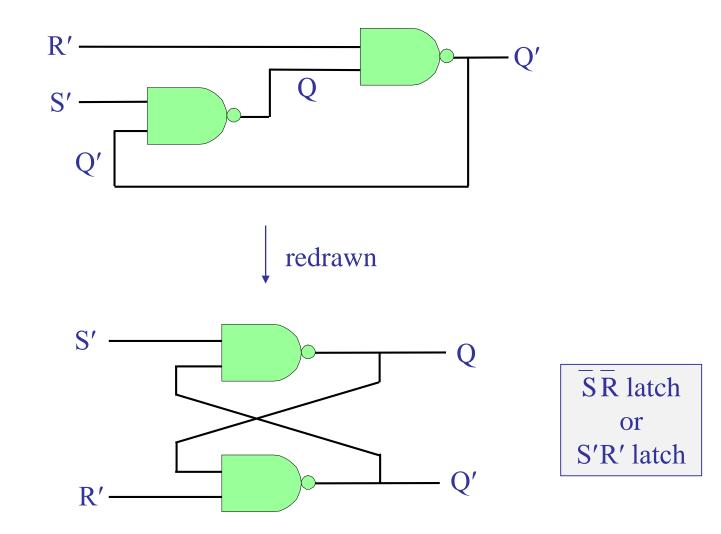

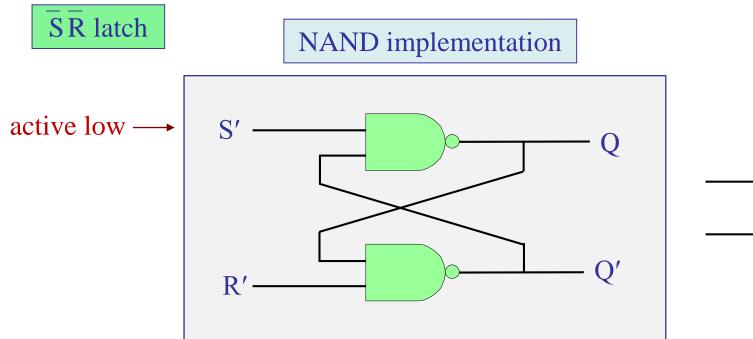

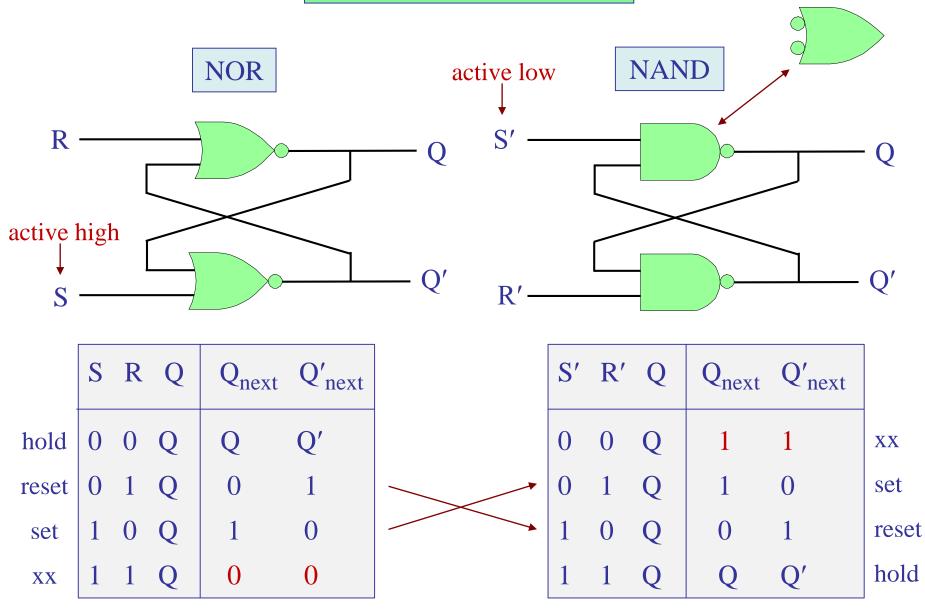

## SR latches – NOR and NAND realizations

using De Morgan duality theorem:  $F(X,Y,Z,...)' = F_{dual}(X',Y',Z',...)$

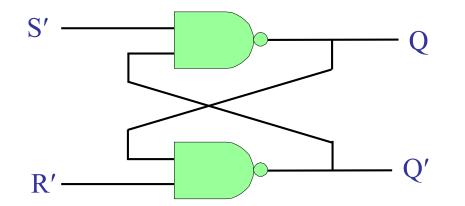

|                                    | S' | R' | Q | Q <sub>next</sub> | Q' <sub>next</sub> |

|------------------------------------|----|----|---|-------------------|--------------------|

| not allowed                        | 0  | 0  | Q | 1                 | 1                  |

| active low $\longrightarrow$ set   | 0  | 1  | Q | 1                 | 0                  |

| active low $\longrightarrow$ reset | 1  | 0  | Q | 0                 | 1                  |

| hold                               | 1  | 1  | Q | Q                 | Q′                 |

## characteristic equation

$$Q_{next} = S + R' Q$$

$$Q_{next} = (S' (R' Q)')'$$

### characteristic table

#### characteristic table

|             | S' | R' | Q | Q <sub>next</sub> | Q' <sub>next</sub> |

|-------------|----|----|---|-------------------|--------------------|

| not allowed | 0  | 0  | Q | 1                 | 1                  |

| set         | 0  | 1  | Q | 1                 | 0                  |

| reset       | 1  | 0  | Q | 0                 | 1                  |

| hold        | 1  | 1  | Q | Q                 | Q′                 |

### characteristic equation

$$Q_{next} = S + R' Q$$

same K-map as in the NOR case

SR latches - Summary

characteristic tables – in both cases, set means Q=1, reset, Q=0

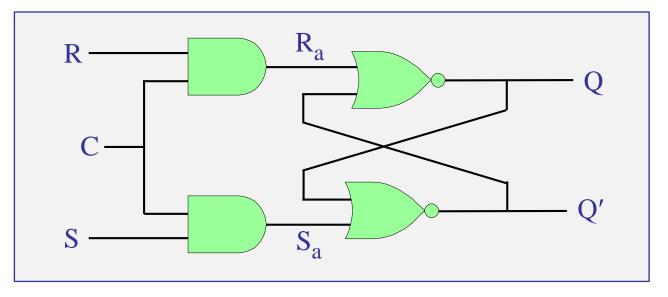

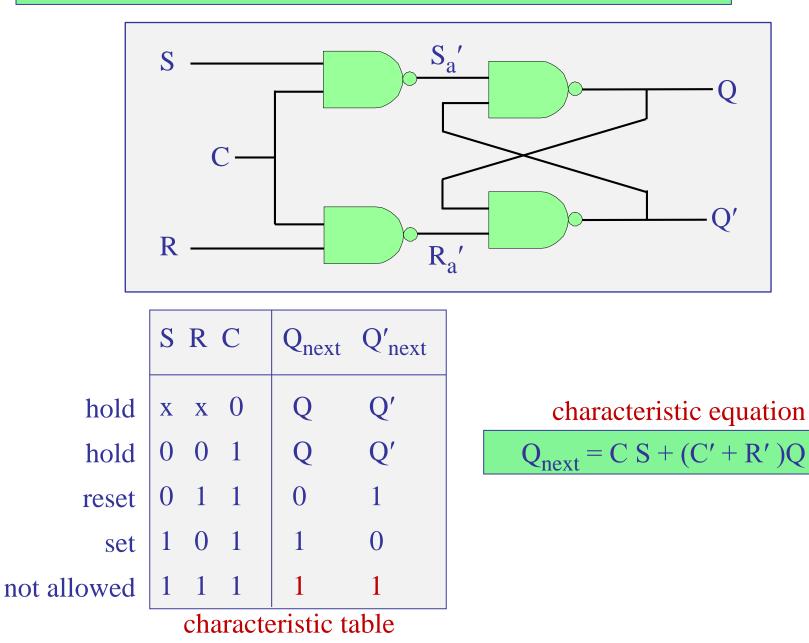

## SR latch – with enable/control/clock signal – NOR version

|                      | S | R | С | Q <sub>next</sub> | Q' <sub>next</sub> |  |

|----------------------|---|---|---|-------------------|--------------------|--|

| hold                 | X | X | 0 | Q                 | Q′                 |  |

| hold                 | 0 | 0 | 1 | Q                 | Q′                 |  |

| reset                | 0 | 1 | 1 | 0                 | 1                  |  |

| set                  | 1 | 0 | 1 | 1                 | 0                  |  |

| not allowed          | 1 | 1 | 1 | 0                 | 0                  |  |

| characteristic table |   |   |   |                   |                    |  |

characteristic equation

$$Q_{next} = C R' S + C' Q + R' Q$$

$R_a = C R$

$S_a = C R$

$S_a = C S$

$Q_{next} = R_a' S_a + R_a' Q$

## SR latch – with enable/control/clock signal – NAND version

#

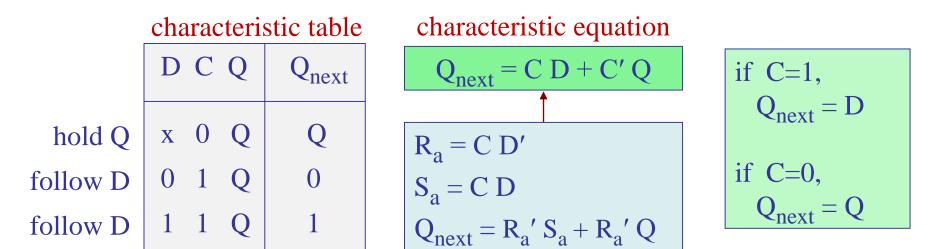

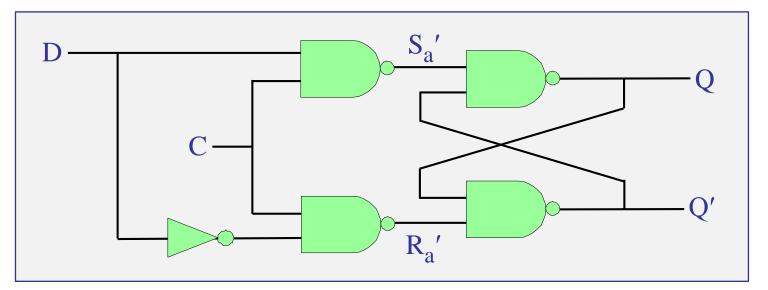

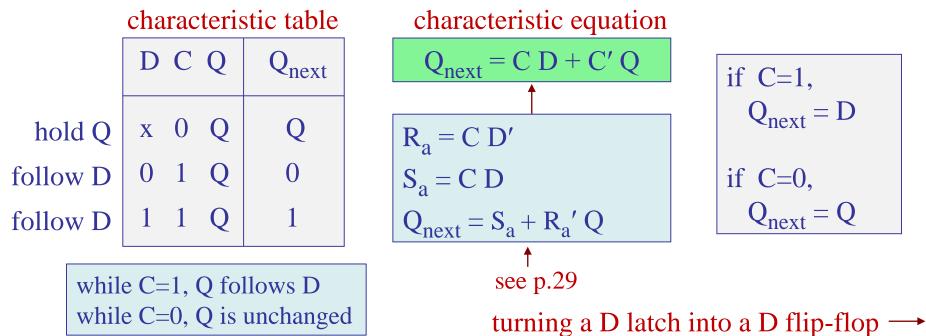

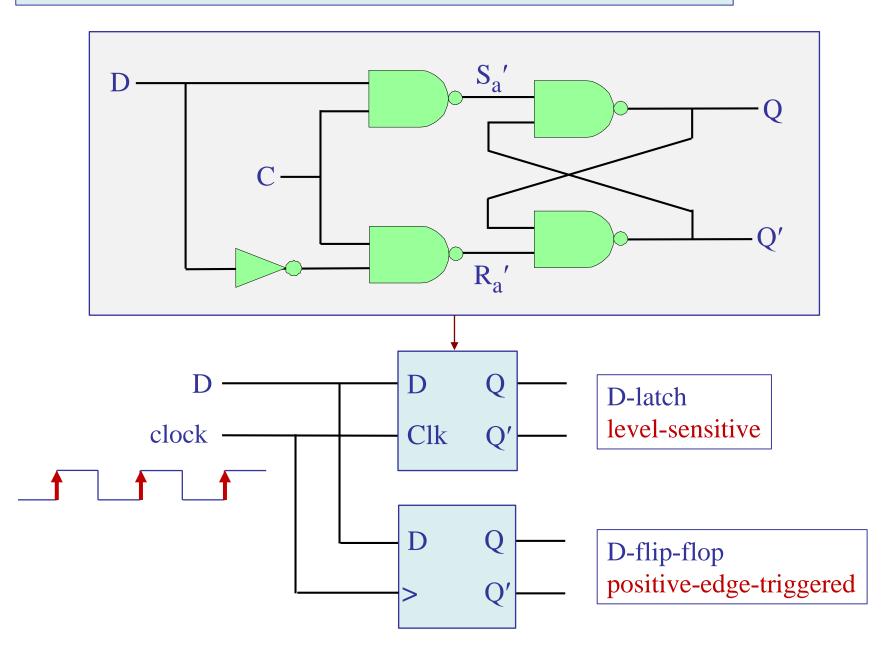

i.e., Q follows D while C=1, otherwise Q remains unchanged

$R_a = C D'$  $S_a = C D$  $Q_{next} = R_a' S_a + R_a' Q$ = (C D')' (CD) + (C D')' Q= (C' + D) (CD) + (C' + D) Q= C' CD + D C D + C' Q + D Q= C D + C' Q + D Q= C D + C' Q(by consensus theorem)

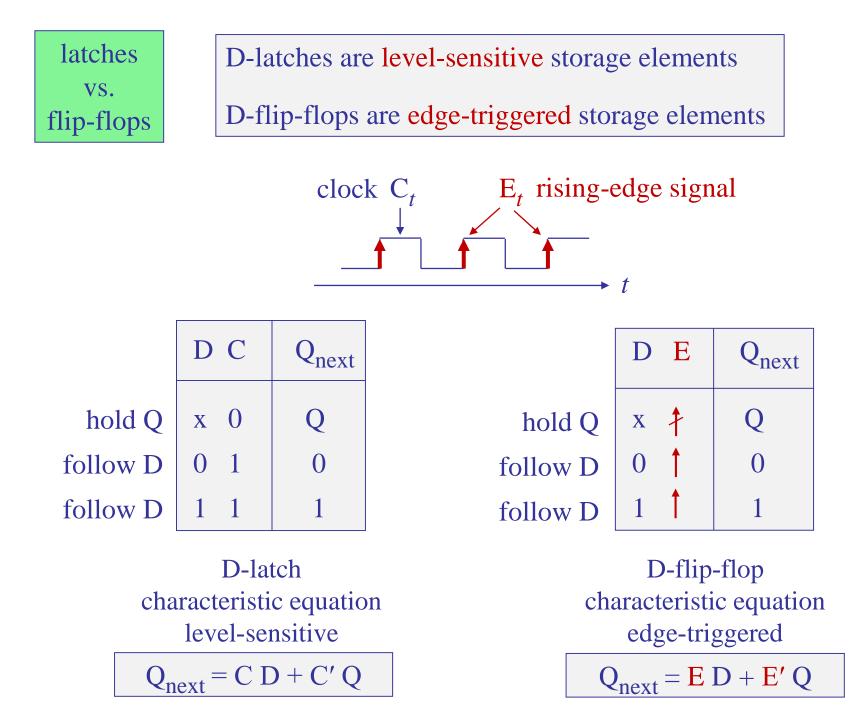

D latch

## D latch

## NAND implementation

follow D

1

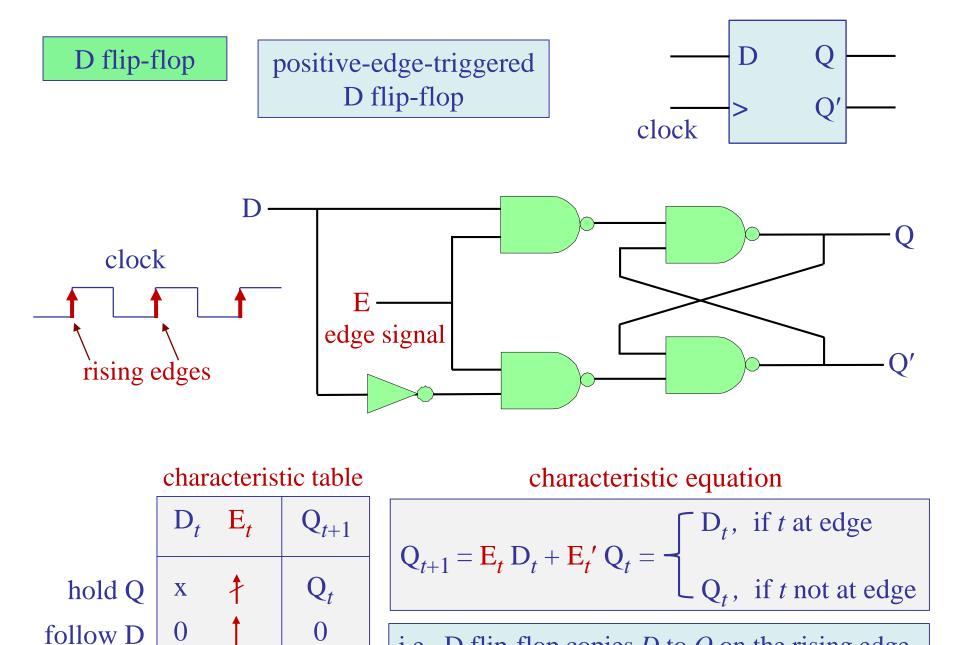

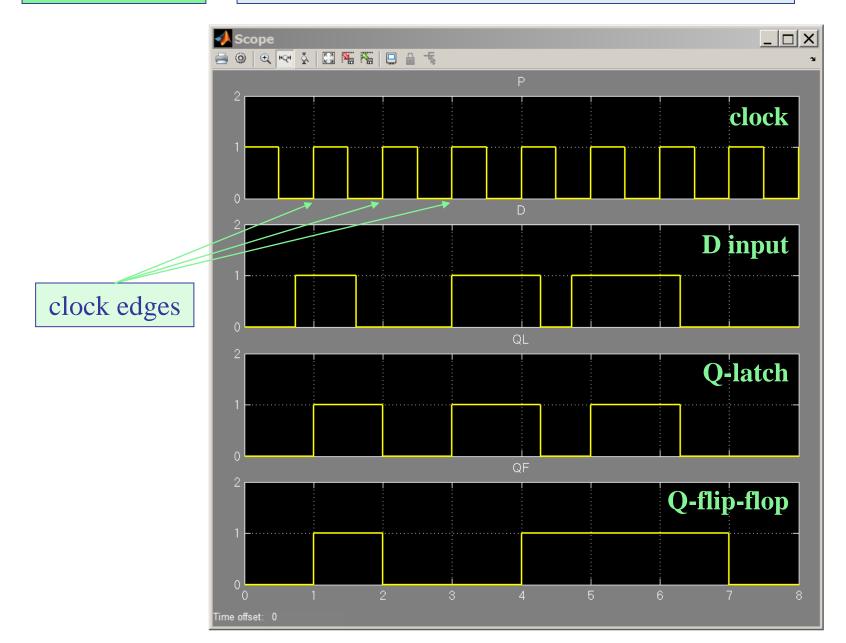

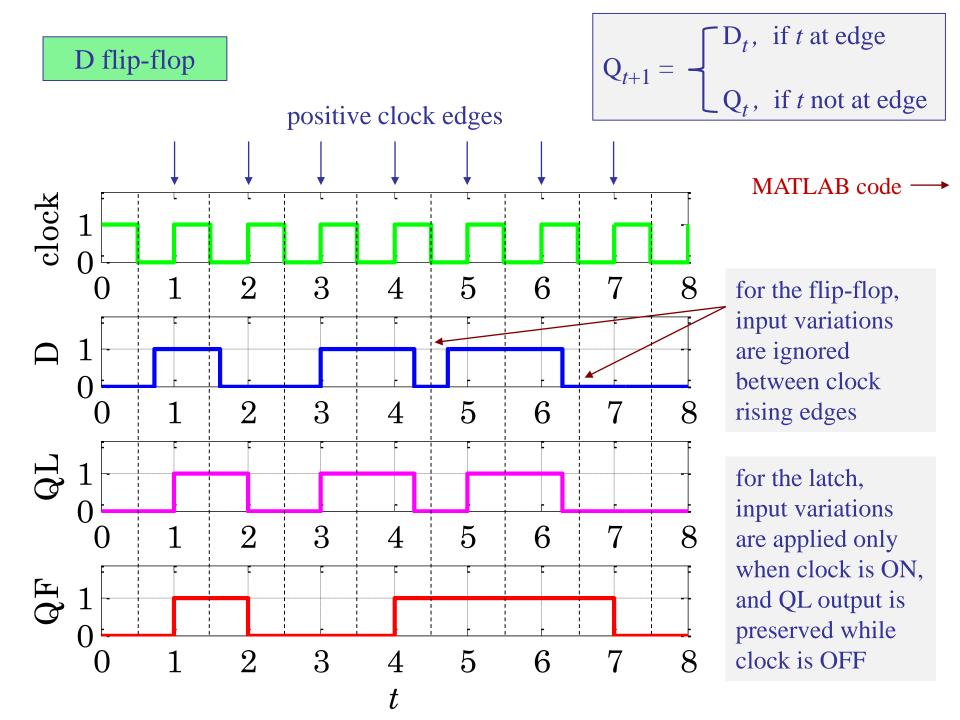

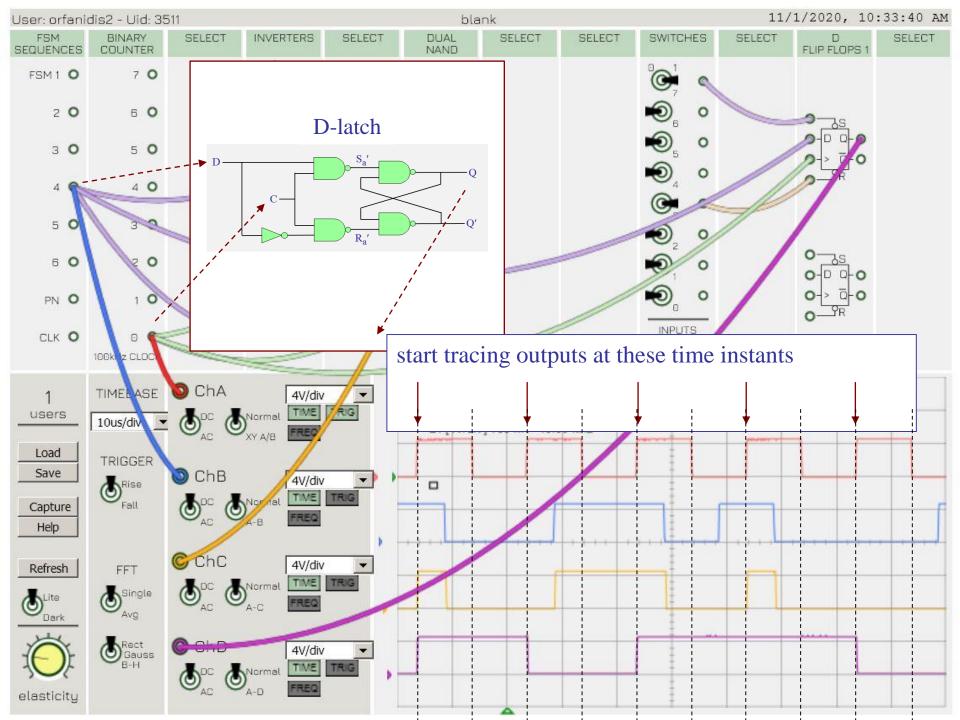

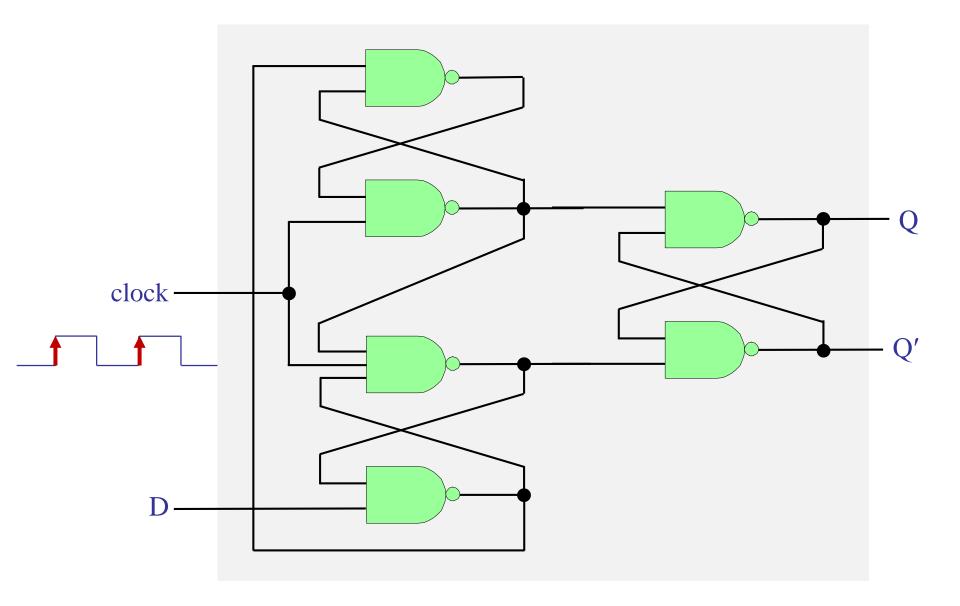

i.e., D flip-flop copies D to Q on the rising edge of the clock, and remembers Q at all other times

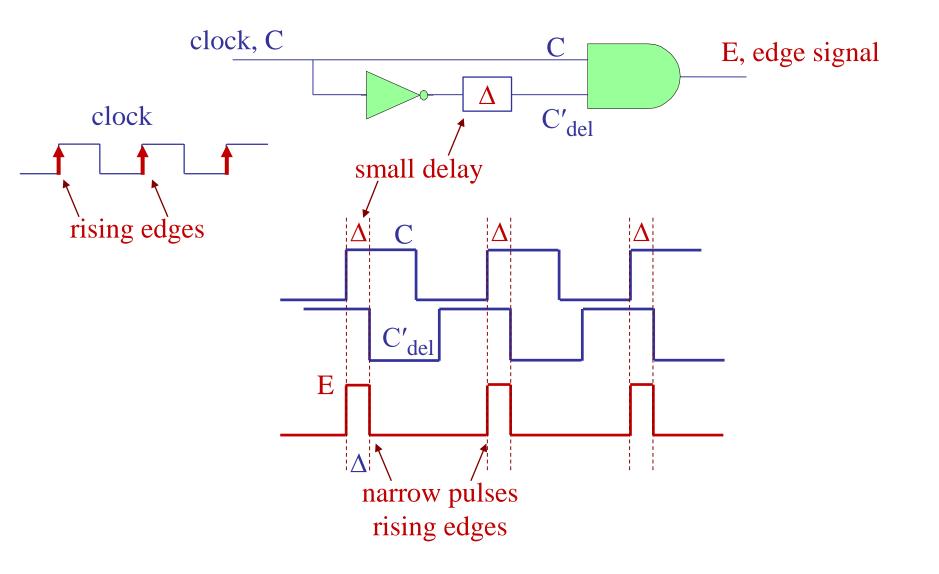

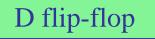

edge-detector – generating an edge signal from the clock

D flip-flop

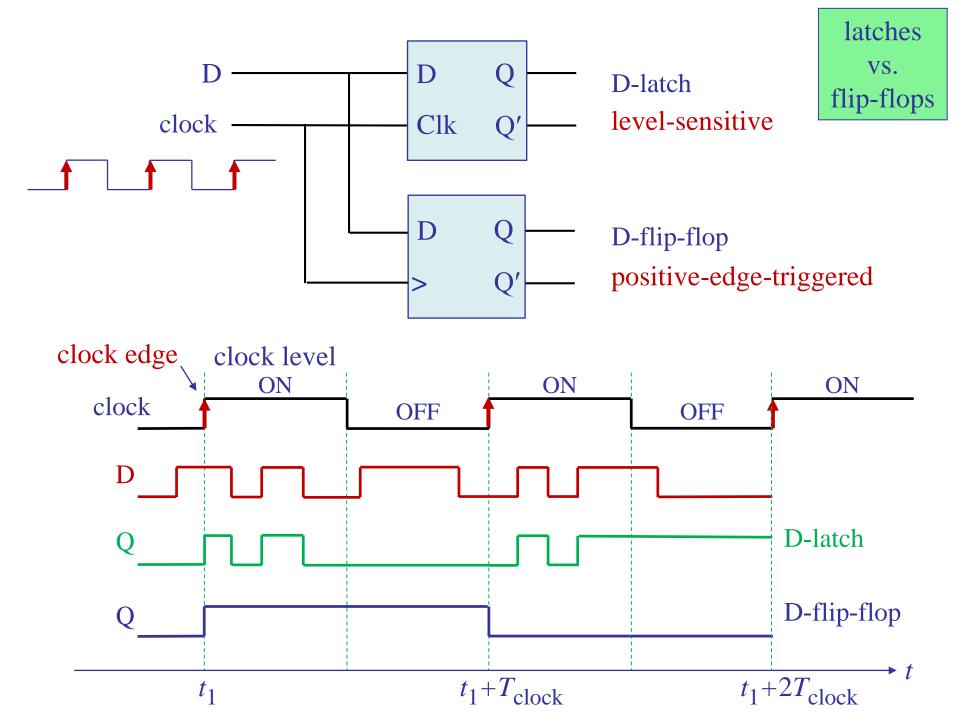

## D flip-flop positive-edge-triggered D flip-flop vs. D latch

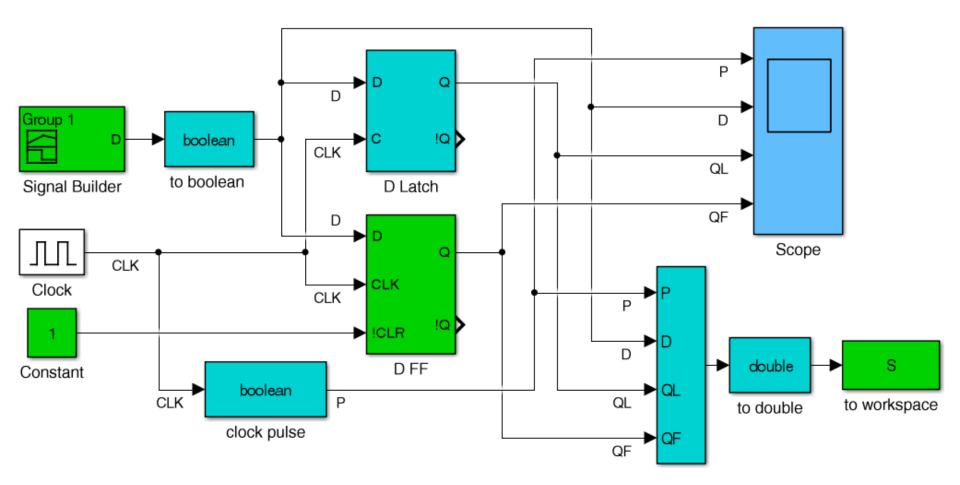

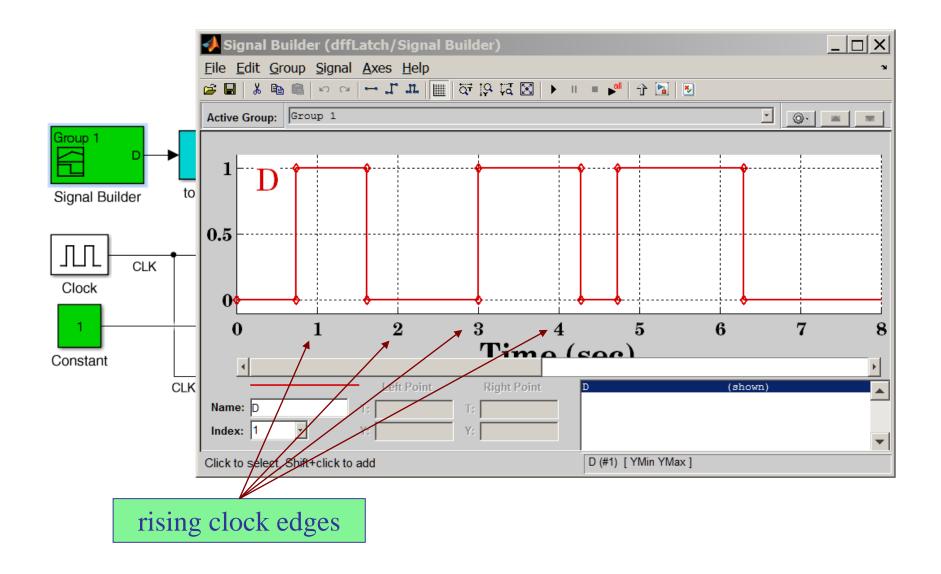

DffLs.slx file on Canvas

#### flip-flops and clock are found in Simulink library under Simulink extras/flip flops

#### positive-edge-triggered D flip-flop vs. D latch

D flip-flop

## D flip-flop

#### positive-edge-triggered D flip-flop vs. D latch

#### D flip-flop

```

%% DffLm.m - D flip-flop vs. D latch - on Canvas

% run DffLs.slx first to generate structure S

t = S.time; % time

P = S.data(:,1); % clock pulse

D = S.data(:,2); % D input

QL = S.data(:,3); % latch output

QF = S.data(:,4); % flip-flop output

set(0, 'DefaultAxesFontSize',14);

figure;

subplot(4,1,1); stairs(t,P,'g-','linewidth',2);

xaxis(0,8,0:8); yaxis(0,1.9,0:1); ylabel('clock')

subplot(4,1,2); stairs(t,D,'b-','linewidth',2);

xaxis(0,8,0:8); yaxis(0,1.9,0:1); ylabel('D'); grid

subplot(4,1,3); stairs(t,QL,'m-','linewidth',2);

xaxis(0,8,0:8); yaxis(0,1.9,0:1); ylabel('QL'); grid

subplot(4,1,4); stairs(t,QF,'r-','linewidth',2);

xaxis(0,8,0:8); yaxis(0,1.9,0:1); ylabel('QF'); grid

xlabel('{\itt}')

```

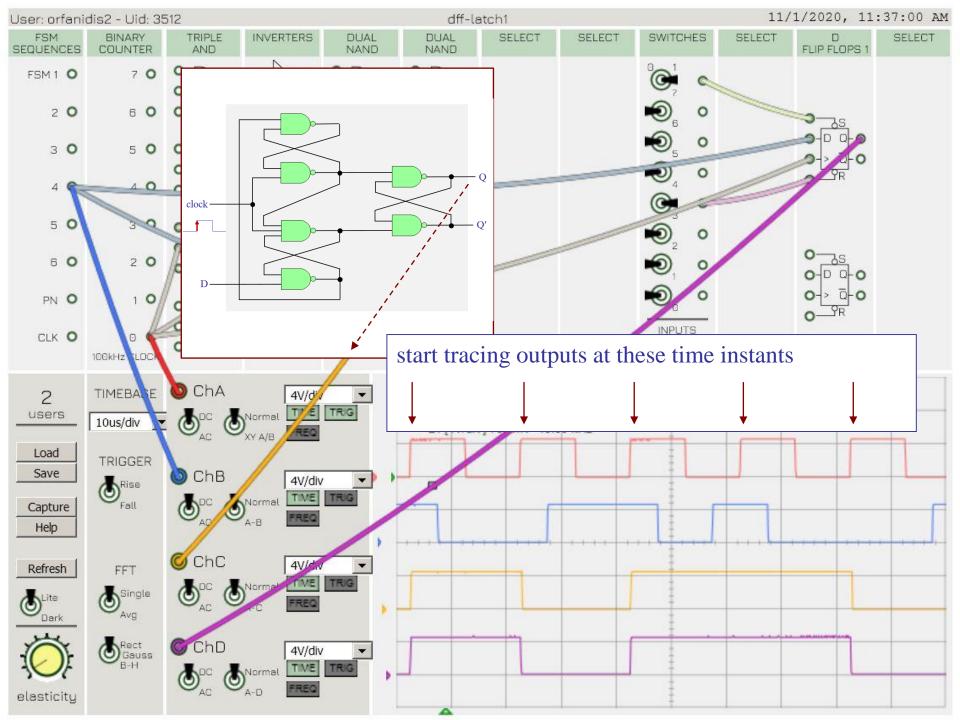

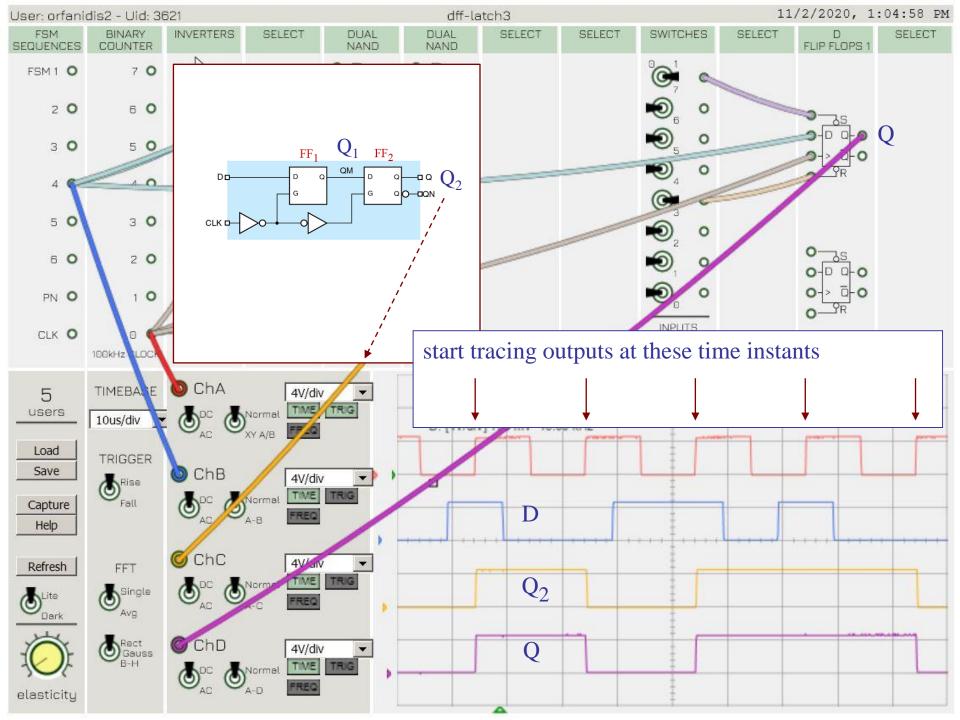

Emona lab 5 experiment – comparing D-latches with D-flip-flops

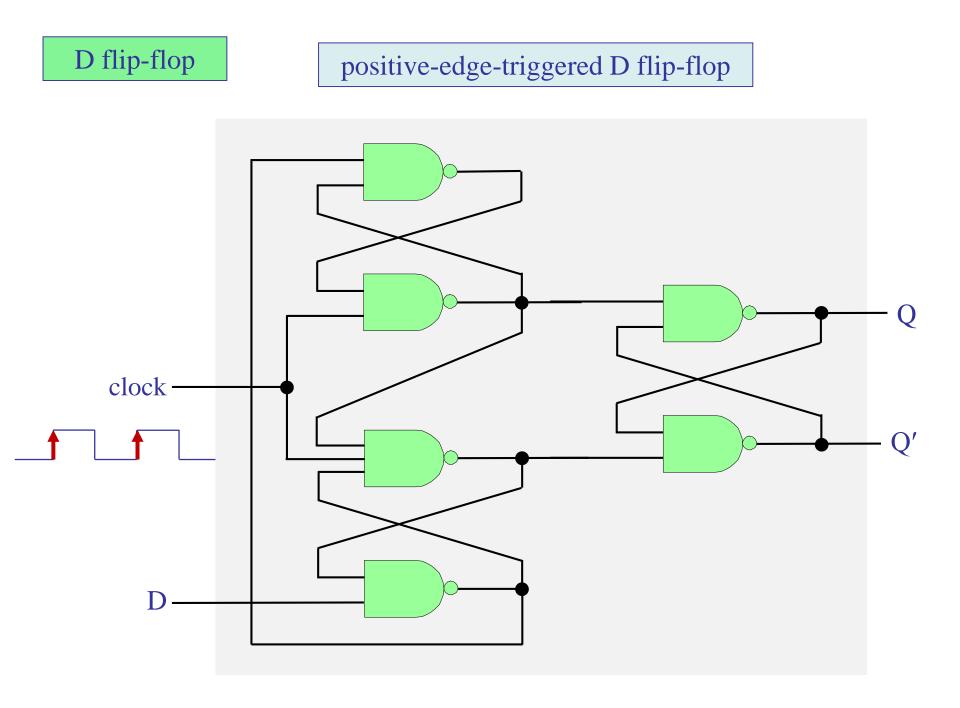

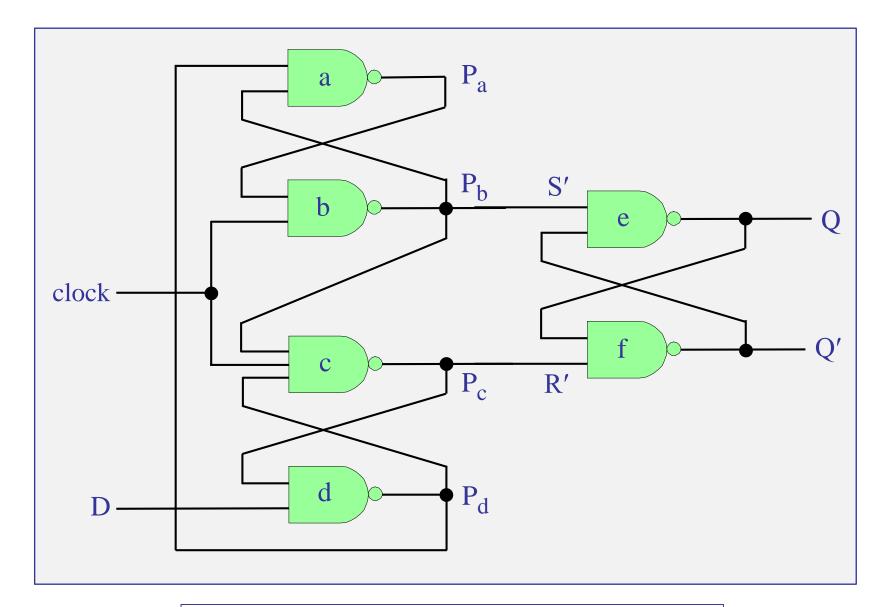

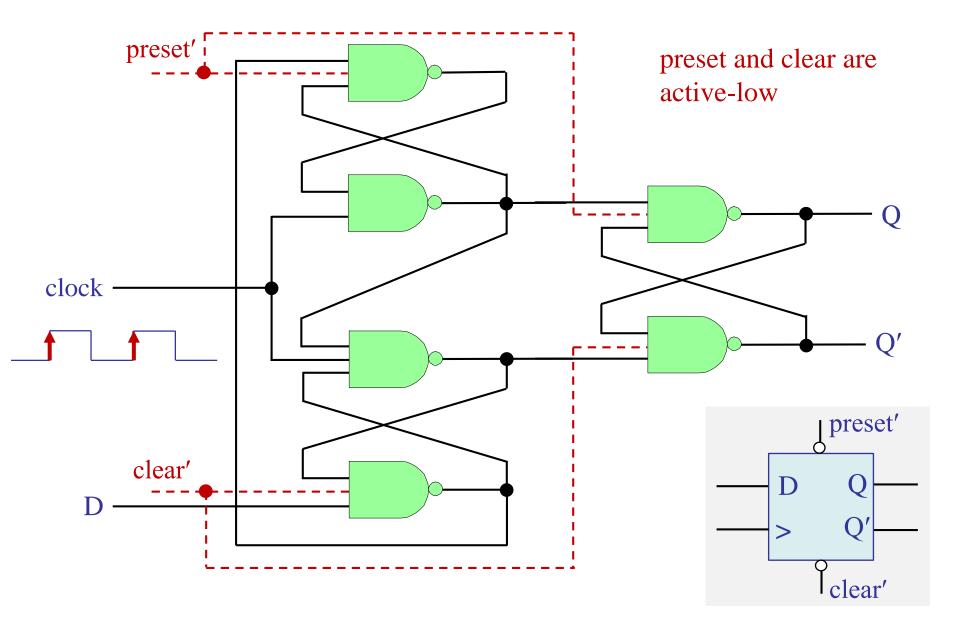

See next page for an explanation of its operation with the help of the truth-table of an S'R' latch. It will be explored further in the DLD lab (lab5). When clock = 0, the outputs of gates b & c are  $P_b = P_c = 1$ , which maintains the output latch (gates e & f) in its present state. In addition,  $P_d = D'$  and  $P_a = D$ .

When the clock changes to clock = 1, then, the values of  $P_a$  and  $P_d$  are transmitted through gates b & c to cause  $P_b = D'$  and  $P_c = D$ , thus, resulting in, Q = D and Q' = D'.

After *clock* changes to 1, any further changes in D should not affect the output latch, as long as, clock = 1. There are two possibilities:

(a) if D = 0 at the **positive edge** of the clock, then,  $P_c = 0$ , keeping the output  $P_d = 1$ , as long as, *clock* = 1, regardless of the value of the D input, and maintaining  $Q = 0 = D_{edge}$ .

(b) if D = 1 at the positive edge of the clock, then,  $P_b = 0$ , forcing the outputs,  $P_a = 1$ ,  $P_c = 1$ , regardless of the D input, and maintaining the output equal to  $Q = 1 = D_{edge}$ .

Therefore, the flip-flop ignores changes in the D input, while clock = 1. Hence, the circuit behaves as a positive-edge-triggered flip-flop.

| S' | R' | Q | Q <sub>next</sub> | Q' <sub>next</sub> |

|----|----|---|-------------------|--------------------|

| 0  | 0  | Q | 1                 | 1                  |

| 0  | 1  | Q | 1                 | 0                  |

| 1  | 0  | Q | 0                 | 1                  |

| 1  | 1  | Q | Q                 | Q′                 |

Emona lab 5 experiment – verifying the six-NAND implementation

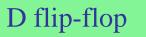

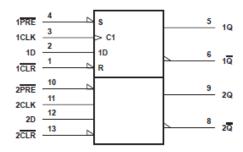

#### (A) MOTOROLA

#### DUAL D-TYPE POSITIVE EDGE-TRIGGERED FLIP-FLOP

The SN54/74LS74A dual edge-triggered flip-flop utilizes Schottky TTL circuitry to produce high speed D-type flip-flops. Each <u>fli</u>p-flop has individual clear and set inputs, and also complementary Q and Q outputs.

Information at input D is transferred to the Q output on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level of the clock pulse and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the HIGH or the LOW level, the D input signal has no effect.

LOGIC DIAGRAM (Each Flip-Flop)

#### SN54/74LS74A

DUAL D-TYPE POSITIVE EDGE-TRIGGERED FLIP-FLOP

LOW POWER SCHOTTKY

#### D flip-flop ICs

54LS74 74LS74

### from Motorola, TI, Fairchild

| MODE SELECT — TRUTH TABLE | MODE | SELECT - | - TRUTH | TABLE |

|---------------------------|------|----------|---------|-------|

|---------------------------|------|----------|---------|-------|

| OPERATING MODE   | INPUTS          |                |     | OUTPUTS |   |

|------------------|-----------------|----------------|-----|---------|---|

| OPERATING MODE   | \$ <sub>D</sub> | s <sub>D</sub> | D   | ø       | q |

| Set              | L               | н              | Х   | н       | L |

| Reset (Clear)    | н               | L              | X   | L       | н |

| *Undetermined    | L               | L              | х   | н       | н |

| Load "1" (Set)   | н               | н              | h   | н       | L |

| Load "0" (Reset) | н               | н              | - I | L       | н |

\* Bgh outputs will be HIGH while both S<sub>D</sub> and C<sub>D</sub> are LOW, but the output states are unpredictable If S<sub>D</sub> and C<sub>D</sub> go HIGH simultaneously. If the levels at the set and clear are near V<sub>IL</sub> maximum then we cannot guarantee to meet the minimum level for V<sub>OH</sub>.

H, h - HIGH Voltage Level

L, I = LOW Voltage Level

X = Don't Care

I, h (q) - Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the HIGH to LOW clock transition.

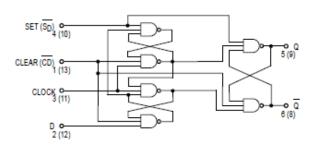

#### SN54ALS74A, SN54AS74A, SN74ALS74A, SN74AS74A DUAL POSITIVE-EDGE-TRIGGERED D-TYPE FLIP-FLOPS WITH CLEAR AND PRESET SDA5142 - APRIL 1982 - REVISED AUGUST 1995

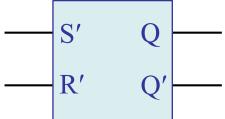

logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the D, J, and N packages.

logic diagram (positive logic)

54LS74 74LS74

D flip-flop ICs

from Motorola, TI, Fairchild

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>‡</sup>

| Supply voltage, V <sub>CC</sub><br>Input voltage, V <sub>1</sub>  |                |

|-------------------------------------------------------------------|----------------|

| Operating free-air temperature range, T <sub>A</sub> : SN54ALS74A | -55°C to 125°C |

| Storage temperature range                                         |                |

\$ Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

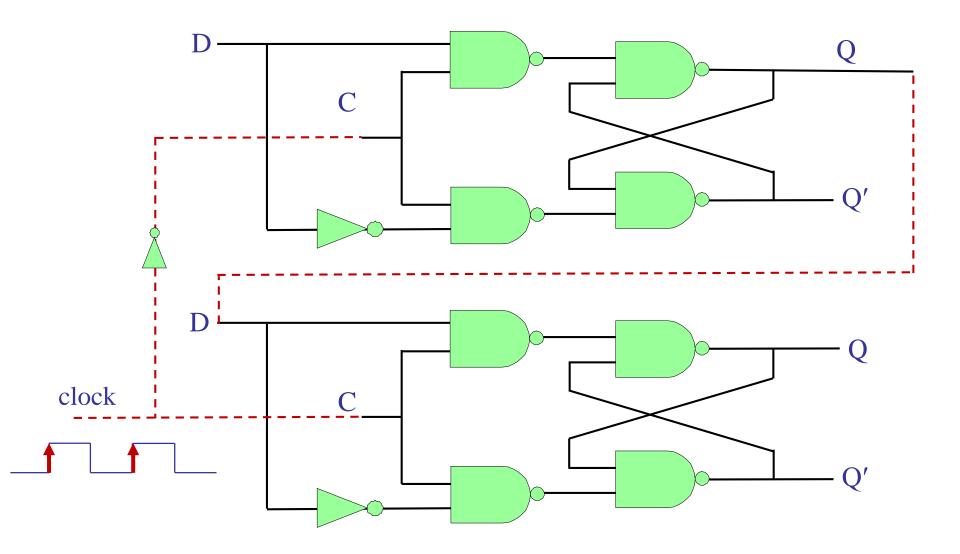

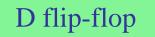

### D flip-flop

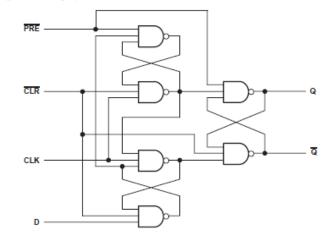

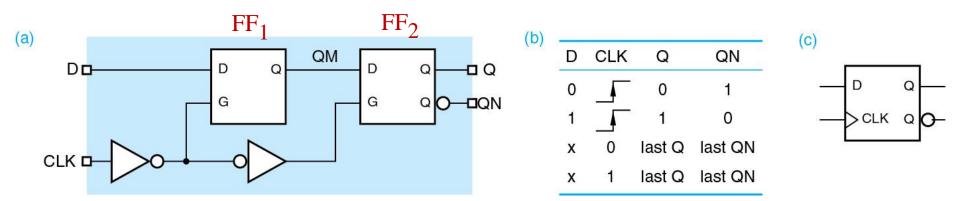

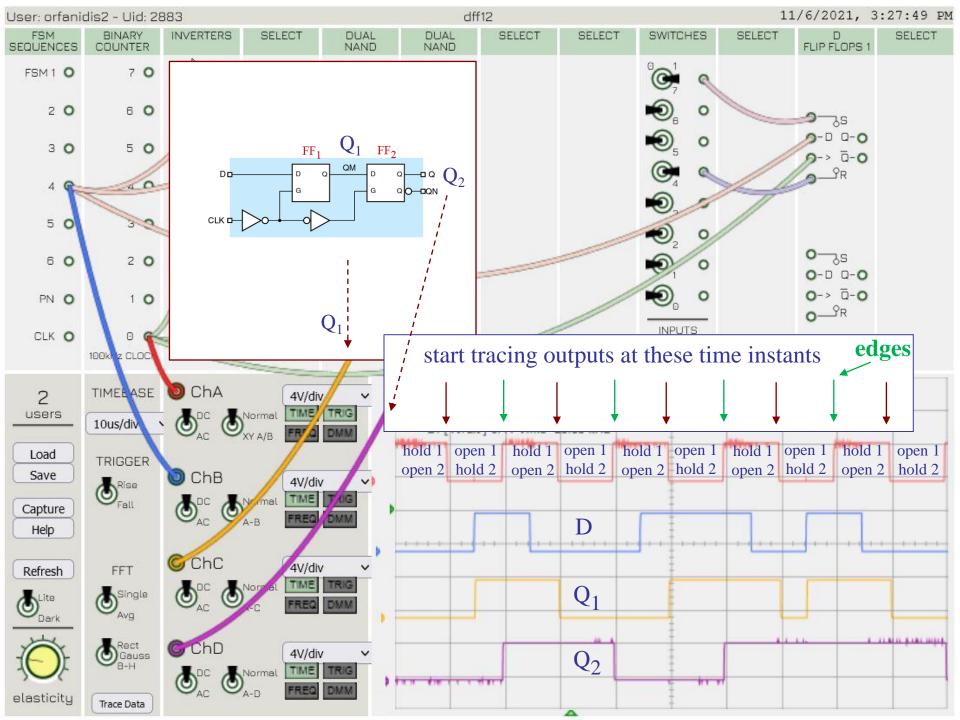

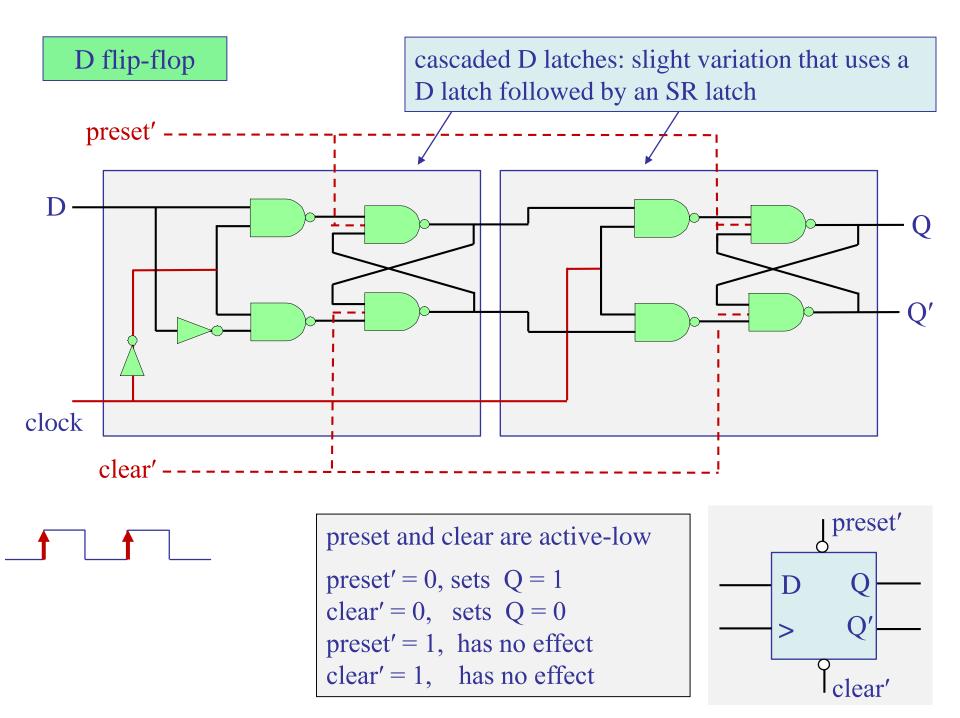

positive-edge-triggered D flip-flop can also be constructed by cascading two D-latches, but driven by opposite clocks, see Wakerly, Sect. 10.2.4

when CLK = 0,  $FF_1$  is open and follows its input, D

when CLK = 1,  $FF_1$  is closed and its current output QM is transferred to  $FF_2$ 's output Q, and QM is prevented from changing until CLK=0 again,

$FF_2$  remains open while CLK = 1, but changes only at the rising edge of that interval because  $FF_1$  is closed and not changing during the rest of the interval,

so effectively, D is transferred to Q only at the rising edges (0 to 1) of the clock period and Q maintains its state during the rest of the clock period

# cascading two D-latches together, and tying their control signals to opposite clocks

#### cascaded D latches

This implementation will be explored in lab5, but note however, that the former implementation that uses three SR-latches (p. 53) is slightly more efficient, since it requires six NAND gates instead of eight, and is used in commercially available D-flip-flop ICs (see p. 54-55).

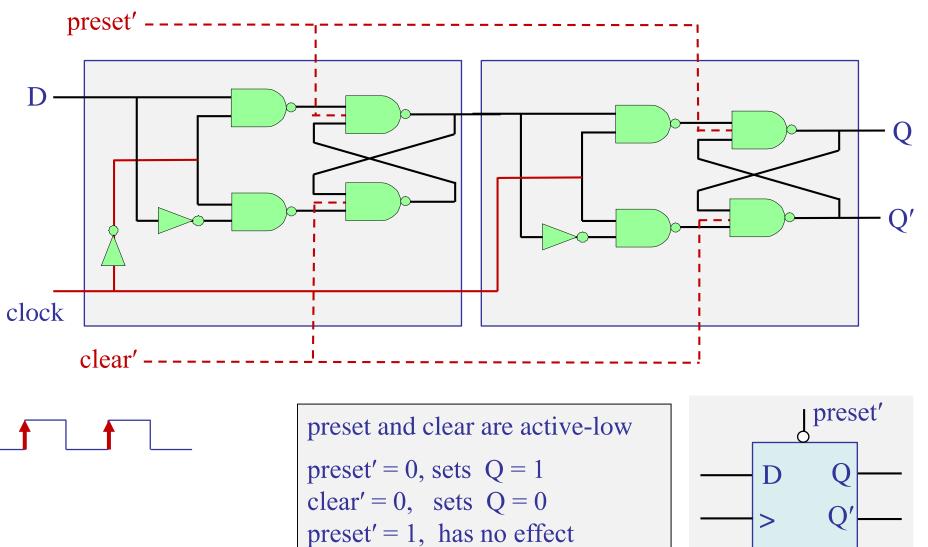

#### D flip-flop

#### adding preset/clear inputs

clear' = 1, has no effect

clear'

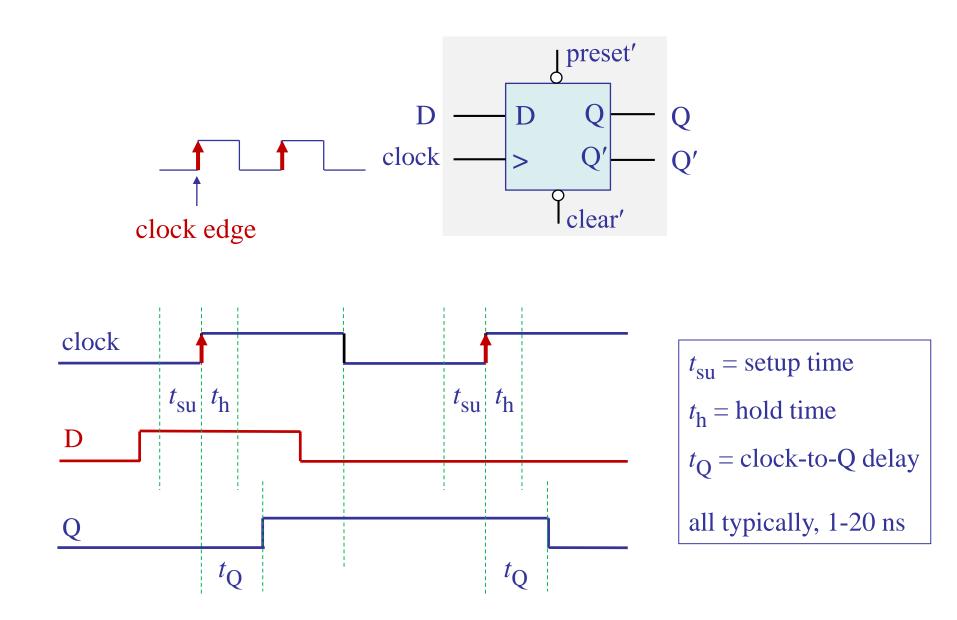

### D flip-flop - timing parameters

#### D flip-flops and State Machines

#### D flip-flops and State Machines

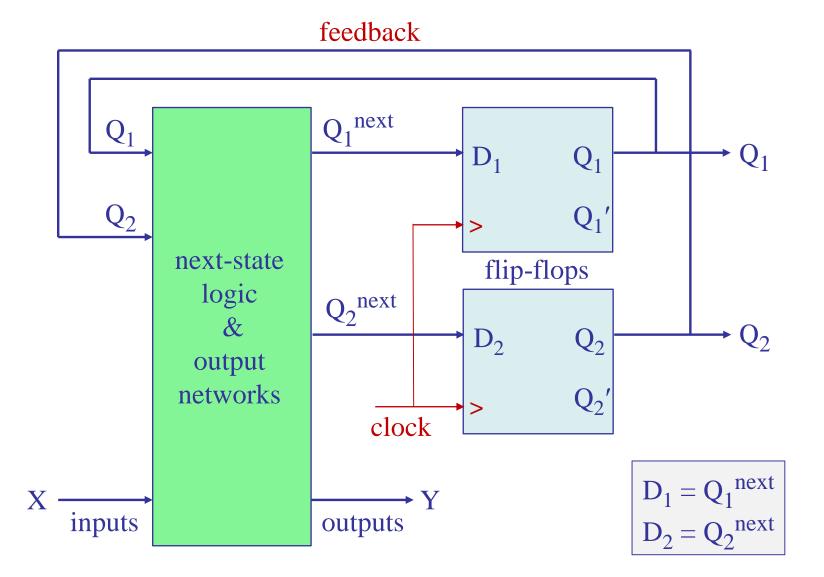

D flip-flops are widely used for the implementation of finite-state machines. Their advantage is that the next states,  $Q^{next}$ , are the excitation inputs to the flip-flops, i.e.,  $D = Q^{next}$ . See next page for an alternative drawing.

D flip-flops and State Machines

#### D flip-flops and State Machines – example with two states

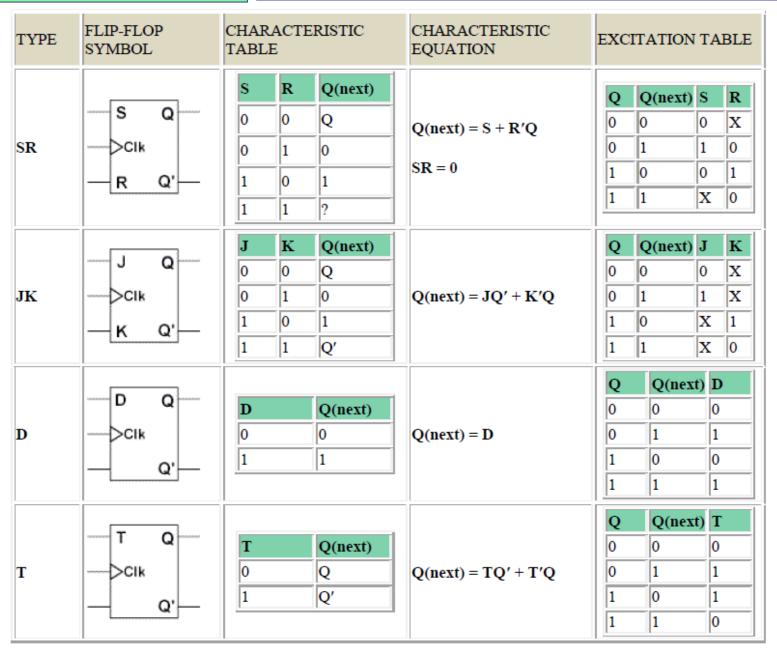

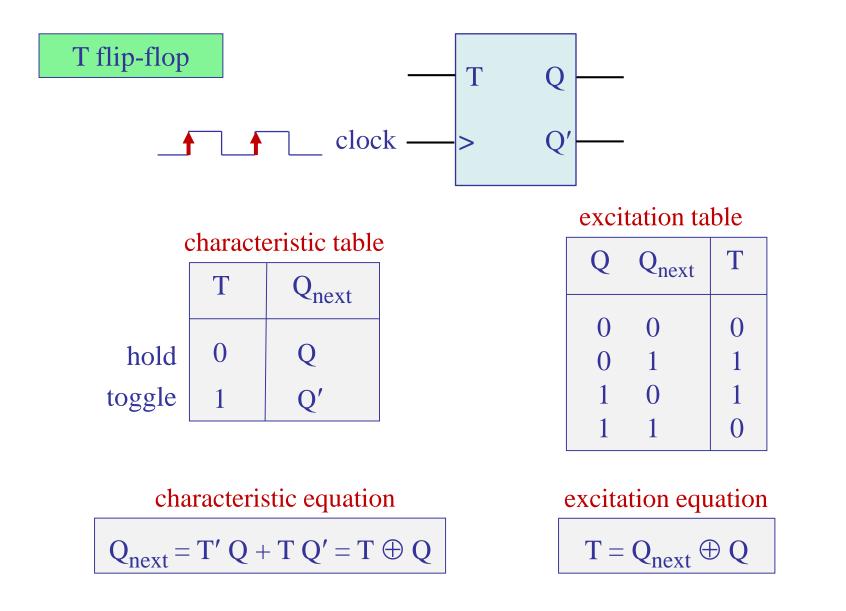

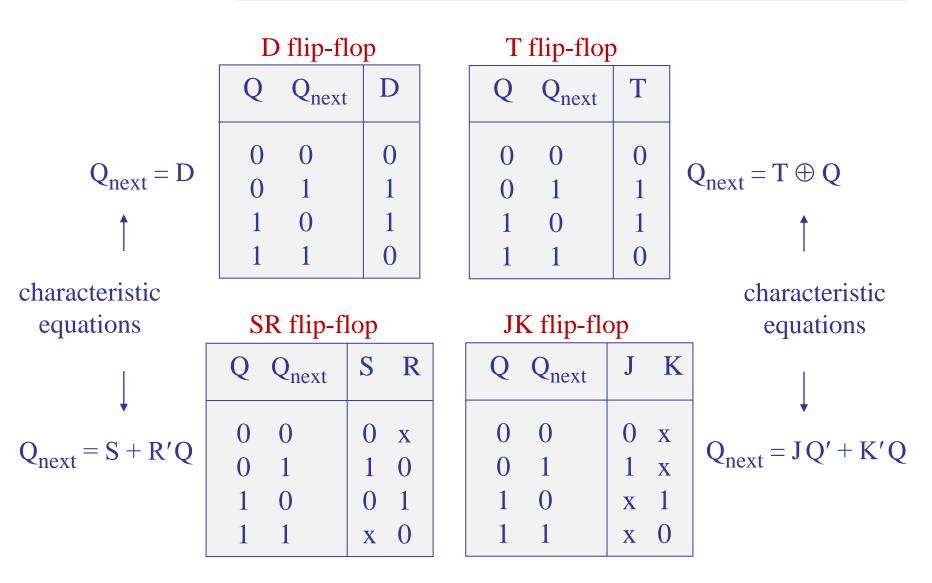

other flip-flop types SR flip-flops T flip-flops JK flip-flops conversions between types characteristic tables characteristic equations excitation tables excitation equations D to JK JK to D D to T T to D JK to T T to JK SR to JK JK to SR

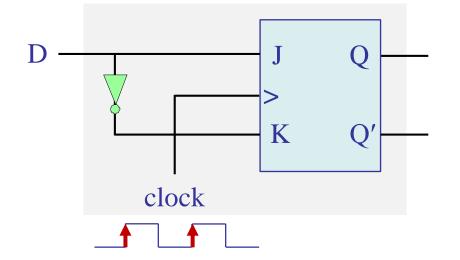

explored in recitations

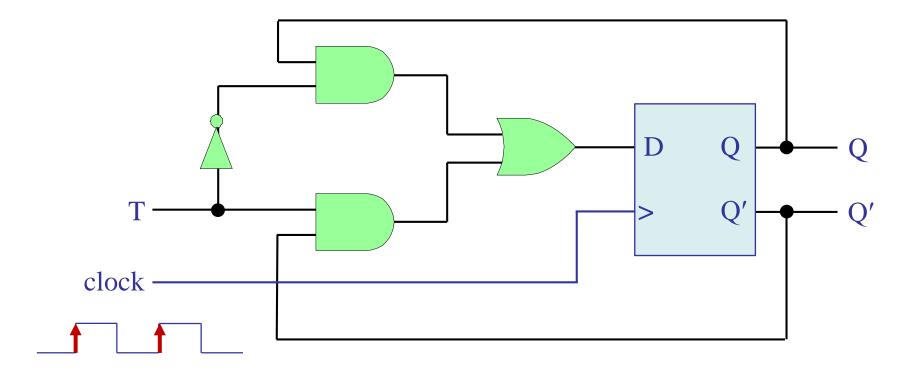

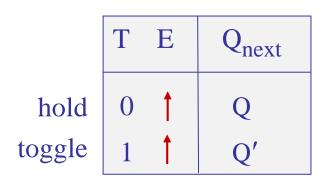

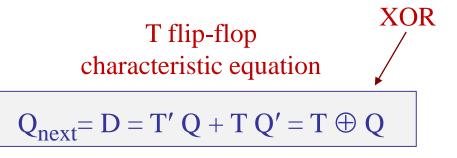

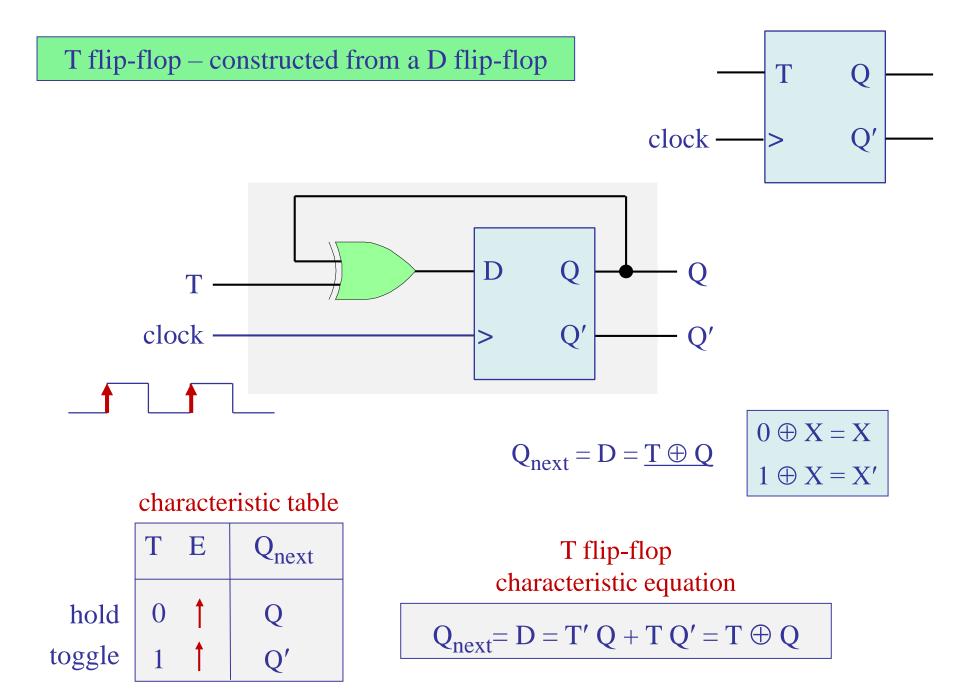

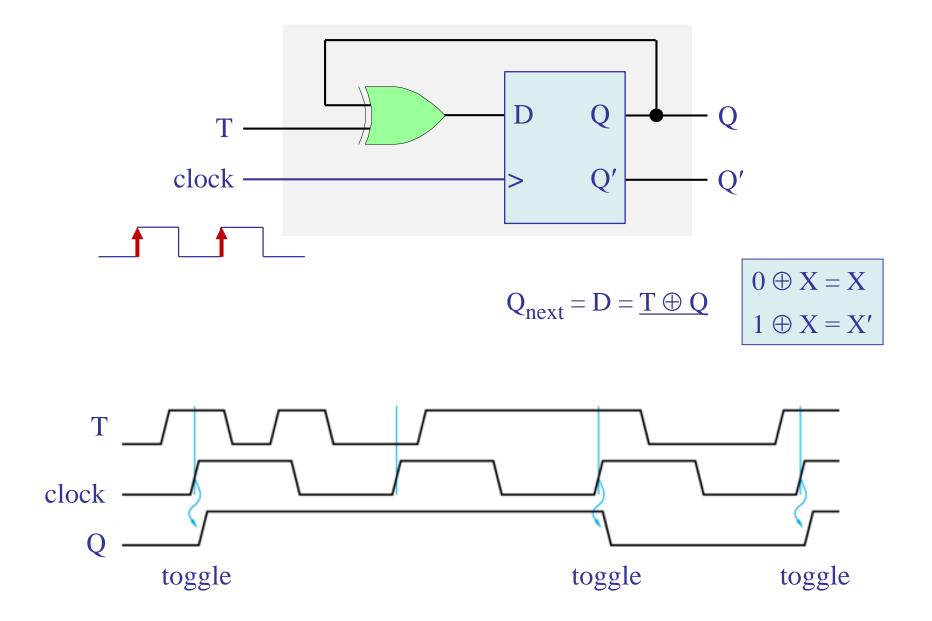

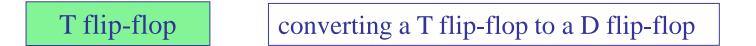

#### T flip-flop – constructed from a D flip-flop

#### T flip-flop – constructed from a D flip-flop

### T flip-flop – constructed from a D flip-flop

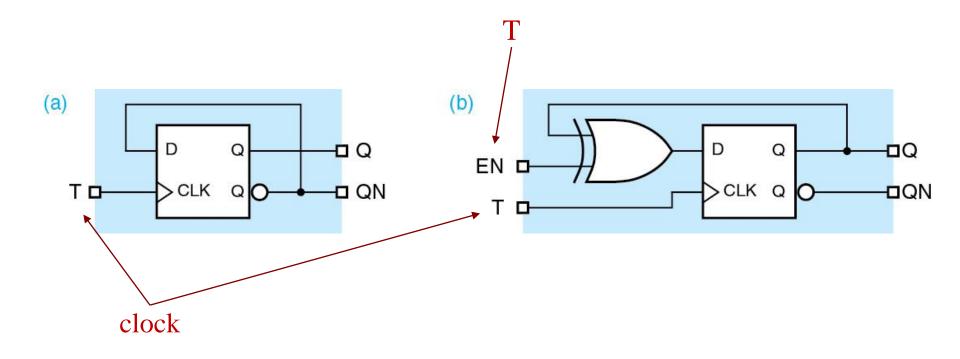

#### Wakerly version

excitation tables are useful because we usually know Q and what  $Q_{next}$  should be, and we need to determine the proper inputs to the flip-flops

$T = D \oplus Q$  $Q_{next} = T \oplus Q = (D \oplus Q) \oplus Q = D$

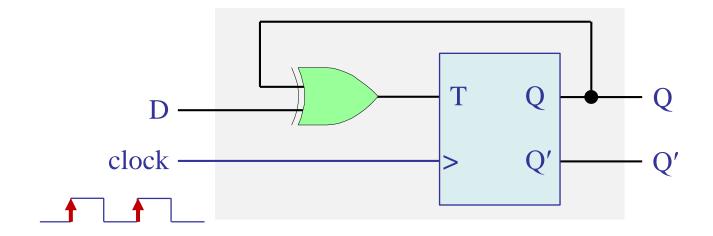

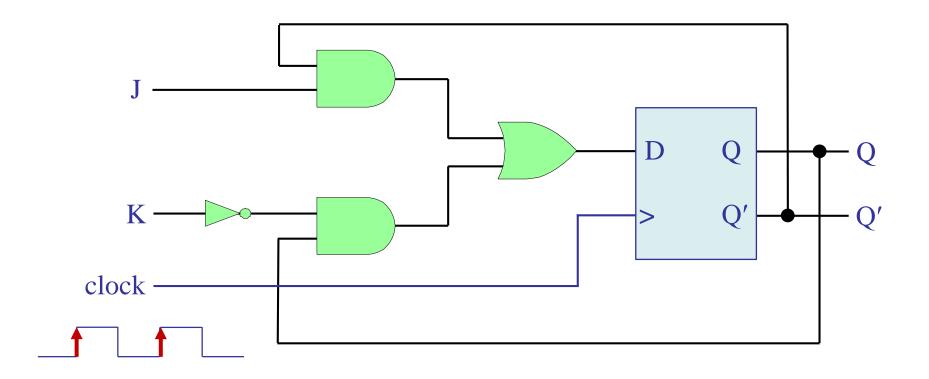

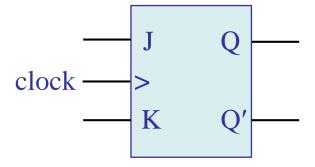

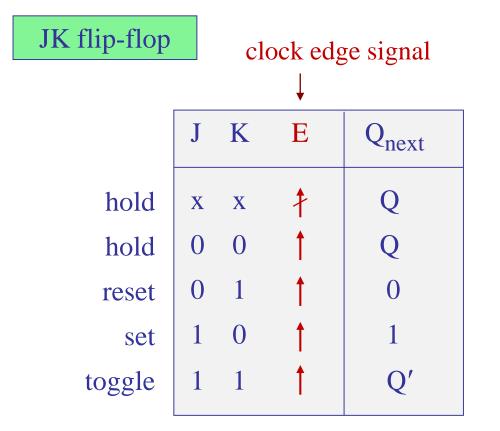

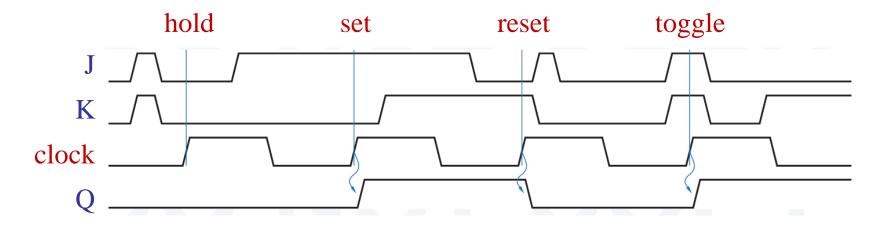

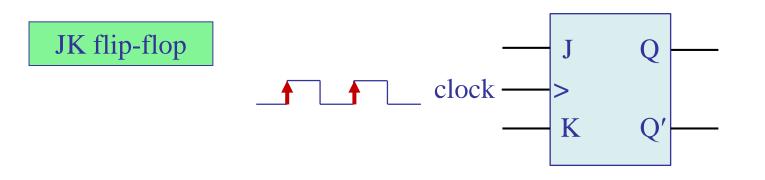

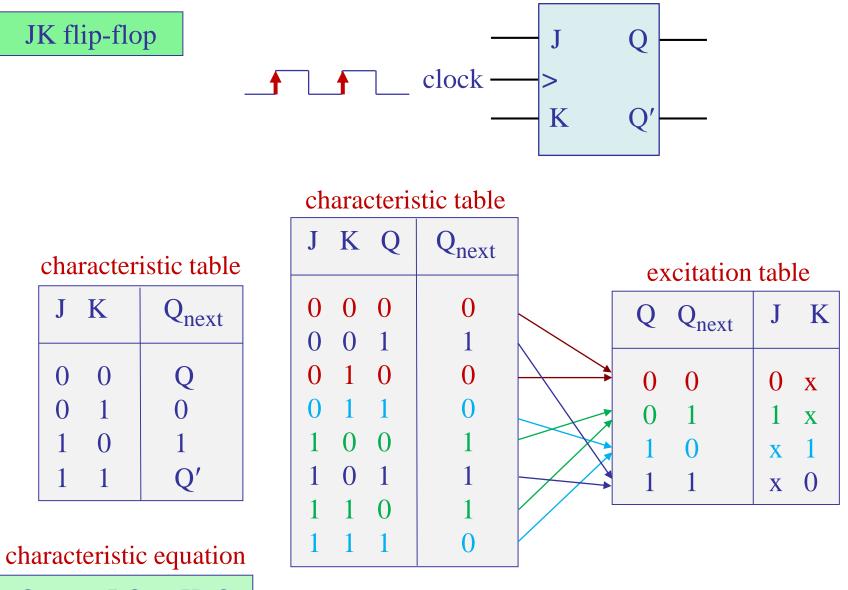

## JK flip-flop

#### positive-edge-triggered JK flip-flop, acts like an SR flip-flop, but toggling when S=R=1

JK flip-flop characteristic equation

$Q_{next} = D = J Q' + K' Q$

$$Q_{next} = J Q' + K' Q$$

characteristic table

| JK                                                                   | Q <sub>next</sub> |

|----------------------------------------------------------------------|-------------------|

| $ \begin{array}{cccc} 0 & 0 \\ 0 & 1 \\ 1 & 0 \\ 1 & 1 \end{array} $ | Q<br>0<br>1<br>Q' |

excitation table

| Q | Q <sub>next</sub> | J | K |

|---|-------------------|---|---|

| 0 | 0                 | 0 | X |

| 0 | 1                 | 1 | Χ |

| 1 | 0                 | X | 1 |

| 1 | 1                 | X | 0 |

characteristic equation

$Q_{next} = J Q' + K' Q$

$Q_{next} = J Q' + K' Q$

$$J = K = T$$

$$Q_{next} = J Q' + K' Q$$

$$Q_{next} = T Q' + T' Q = T \oplus Q$$

$$T - J Q - K Q' - Clock$$

converting a JK flip-flop to a T flip-flop

JK flip-flop

#### converting a JK flip-flop to a D flip-flop

excitation table

J = D K = D'  $Q_{next} = J Q' + K' Q = D Q' + D Q = D$  $Q_{next} = D$

JK flip-flop

| Q | Q <sub>next</sub> | J | K |

|---|-------------------|---|---|

| 0 | 0                 | 0 | X |

| 0 | 1                 | 1 | X |

| 1 | 0                 | X | 1 |

| 1 | 1                 | X | 0 |

#### flip-flop conversions - summary & web links

```

D to JK: D = JQ' + K'Q

JK to D: J = D, K = D'

D to T: D = T \oplus Q

T to D: T=D \oplus Q

JK to T: J = K = T

T to JK: T = JQ' + KQ

SR to JK: S = JQ', R = KQ

JK to SR: J = S, K = R

```

flip-flop conversions - part 1 flip-flop conversions - part 2 flip-flop conversions - part 3 flip-flop conversions - part 4

#### excitation tables

excitation tables are useful because we usually know what Q and  $Q_{next}$  should be, and wish to determine the proper inputs to the flip-flops

## flip-flops - summaryReference: A .F. Kana, DLD lectures (on Canvas)